INTERNATIONAL

STANDARD

ISO / IEC/IEEE

8802-3

Third edition

2021-02

AMENDMENT 9

2021-12

---

---

**Telecommunications and exchange

between information technology

systems — Requirements for local and

metropolitan area networks —**

**Part 3:

Standard for Ethernet**

AMENDMENT 9: Physical layer

specifications and management

parameters for 25 Gb/s and 50 Gb/s

passive optical networks

*Télécommunications et échange entre systèmes informatiques —

Exigences pour les réseaux locaux et métropolitains —*

*Partie 3: Norme pour Ethernet*

*AMENDEMENT 9: Spécifications de couche physique et paramètres de

gestion pour réseaux optiques passifs à 25 Gb/s et 50 Gb/s*

Reference number

ISO/IEC/IEEE 8802-3:2021/Amd.9:2021(E)

© IEEE 2020

**COPYRIGHT PROTECTED DOCUMENT**

© IEEE 2020

All rights reserved. Unless otherwise specified, or required in the context of its implementation, no part of this publication may be reproduced or utilized otherwise in any form or by any means, electronic or mechanical, including photocopying, or posting on the internet or an intranet, without prior written permission. Permission can be requested from IEEE at the address below.

Institute of Electrical and Electronics Engineers, Inc

3 Park Avenue, New York

NY 10016-5997, USA

Email: [stds.ipr@ieee.org](mailto:stds.ipr@ieee.org)

Website: [www.ieee.org](http://www.ieee.org)

Published in Switzerland

## Foreword

ISO (the International Organization for Standardization) and IEC (the International Electrotechnical Commission) form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC participate in the development of International Standards through technical committees established by the respective organization to deal with particular fields of technical activity. ISO and IEC technical committees collaborate in fields of mutual interest. Other international organizations, governmental and non-governmental, in liaison with ISO and IEC, also take part in the work.

The procedures used to develop this document and those intended for its further maintenance are described in the ISO/IEC Directives, Part 1. In particular, the different approval criteria needed for the different types of ISO/IEC documents should be noted. This document was drafted in accordance with the editorial rules of the ISO/IEC Directives, Part 2 (see [www.iso.org/directives](http://www.iso.org/directives) or [www.iec.ch/members\\_experts/refdocs](http://www.iec.ch/members_experts/refdocs)).

IEEE Standards documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. The IEEE develops its standards through a consensus development process, approved by the American National Standards Institute, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and serve without compensation. While the IEEE administers the process and establishes rules to promote fairness in the consensus development process, the IEEE does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO and IEC shall not be held responsible for identifying any or all such patent rights. Details of any patent rights identified during the development of the document will be in the Introduction and/or on the ISO list of patent declarations received (see [www.iso.org/patents](http://www.iso.org/patents)) or the IEC list of patent declarations received (see [patents.iec.ch](http://patents.iec.ch)).

Any trade name used in this document is information given for the convenience of users and does not constitute an endorsement.

For an explanation of the voluntary nature of standards, the meaning of ISO specific terms and expressions related to conformity assessment, as well as information about ISO's adherence to the World Trade Organization (WTO) principles in the Technical Barriers to Trade (TBT), see [www.iso.org/iso/foreword.html](http://www.iso.org/iso/foreword.html). In the IEC, see [www.iec.ch/understanding-standards](http://www.iec.ch/understanding-standards).

ISO/IEC/IEEE 8802-3:2021/Amd 9 was prepared by the LAN/MAN of the IEEE Computer Society (as [IEEE Std 802.3 ca<sup>TM</sup> -2020]) and drafted in accordance with its editorial rules. It was adopted, under the "fast-track procedure" defined in the Partner Standards Development Organization cooperation agreement between ISO and IEEE, by Joint Technical Committee ISO/IEC JTC 1, *Information technology*, Subcommittee SC 6, *Telecommunications and information exchange between systems*.

A list of all parts in the ISO/IEC/IEEE 8802 series can be found on the ISO and IEC websites.

Any feedback or questions on this document should be directed to the user's national standards body. A complete listing of these bodies can be found at [www.iso.org/members.html](http://www.iso.org/members.html) and [www.iec.ch/national-committees](http://www.iec.ch/national-committees).

STANDARDSISO.COM : Click to view the full PDF of ISO/IEC/IEEE 8802-3:2021/Amd 9:2021

**IEEE Std 802.3ca™-2020**

(Amendment to IEEE Std 802.3™-2018

as amended by IEEE Std 802.3cb™-2018,

IEEE Std 802.3bt™-2018,

IEEE Std 802.3cd™-2018,

IEEE Std 802.3cn™-2019,

IEEE Std 802.3cg™-2019,

IEEE Std 802.3cq™-2020,

IEEE Std 802.3cm™-2020,

and IEEE Std 802.3ch™-2020)

# IEEE Standard for Ethernet

## Amendment 9: Physical Layer Specifications and Management Parameters for 25 Gb/s and 50 Gb/s Passive Optical Networks

Developed by the

**LAN/MAN Standards Committee**

of the

**IEEE Computer Society**

Approved 4 June 2020

**IEEE SA Standards Board**

**Abstract:** This amendment to IEEE Std 802.3-2018 extends the operation of Ethernet passive optical networks (EPONs) to multiple channels of 25 Gb/s providing both symmetric and asymmetric operation for the following data rates (downstream/upstream): 25/10 Gb/s, 25/25 Gb/s, 50/10 Gb/s, 50/25 Gb/s, and 50/50 Gb/s. This standard specifies the 25 Gb/s EPON Multi-Channel Reconciliation Sublayer (MCRS), Nx25G-EPON Physical Coding Sublayers (PCSs), Physical Media Attachment (PMA) sublayers, and Physical Medium Dependent (PMD) sublayers that support both symmetric and asymmetric data rates while maintaining backward compatibility with already deployed 10 Gb/s EPON equipment. Backward compatibility with deployed 1G-EAPON and ITU-T G.984 GPON is maintained with 25GBASE-PQ for the specific case of 1G-EAPON and GPON ONUs using reduced-band (40 nm) lasers. The EPON operation is defined for distances of at least 20 km, and for a split ratio of at least 1:32.

**Keywords:** 25 Gb/s Ethernet passive optical networks (25G-EAPON), 50 Gb/s Ethernet passive optical networks (50G-EAPON), amendment, forward error correction (FEC), IEEE 802.3™, IEEE 802.3ca™, Multi-Channel Reconciliation Sublayer (MCRS), Multipoint MAC Control (MPMC), Physical Coding Sublayer (PCS), Physical Media Attachment (PMA), Physical Medium Dependent (PMD), PON, Point-to-Multipoint (P2MP)

---

The Institute of Electrical and Electronics Engineers, Inc.

3 Park Avenue, New York, NY 10016-5997, USA

Copyright © 2020 by The Institute of Electrical and Electronics Engineers, Inc.

All rights reserved. Published 3 July 2020. Printed in the United States of America.

IEEE and 802 are registered trademarks in the U.S. Patent & Trademark Office, owned by The Institute of Electrical and Electronics Engineers, Incorporated.

PDF: ISBN 978-1-5044-6768-1 STD24221

Print: ISBN 978-1-5044-6769-8 STDPD24221

*IEEE prohibits discrimination, harassment and bullying.*

*For more information, visit <http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html>.*

*No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.*

## Important Notices and Disclaimers Concerning IEEE Standards Documents

IEEE documents are made available for use subject to important notices and legal disclaimers. These notices and disclaimers, or a reference to this page, appear in all standards and may be found under the heading “Important Notices and Disclaimers Concerning IEEE Standards Documents.” They can also be obtained on request from IEEE or viewed at <https://standards.ieee.org/ipr/disclaimers.html>.

### Notice and Disclaimer of Liability Concerning the Use of IEEE Standards Documents

IEEE Standards documents (standards, recommended practices, and guides), both full-use and trial-use, are developed within IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (“IEEE SA”) Standards Board. IEEE (“the Institute”) develops its standards through a consensus development process, approved by the American National Standards Institute (“ANSI”), which brings together volunteers representing varied viewpoints and interests to achieve the final product. IEEE Standards are documents developed through scientific, academic, and industry-based technical working groups. Volunteers in IEEE working groups are not necessarily members of the Institute and participate without compensation from IEEE. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

IEEE Standards do not guarantee or ensure safety, security, health, or environmental protection, or ensure against interference with or from other devices or networks. Implementers and users of IEEE Standards documents are responsible for determining and complying with all appropriate safety, security, environmental, health, and interference protection practices and all applicable laws and regulations.

IEEE does not warrant or represent the accuracy or content of the material contained in its standards, and expressly disclaims all warranties (express, implied and statutory) not included in this or any other document relating to the standard, including, but not limited to, the warranties of: merchantability; fitness for a particular purpose; non-infringement; and quality, accuracy, effectiveness, currency, or completeness of material. In addition, IEEE disclaims any and all conditions relating to: results; and workmanlike effort. IEEE standards documents are supplied “AS IS” and “WITH ALL FAULTS.”

Use of an IEEE standard is wholly voluntary. The existence of an IEEE standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

In publishing and making its standards available, IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity nor is IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing any IEEE Standards document, should rely upon his or her own independent judgment in the exercise of reasonable care in any given circumstances or, as appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE standard.

~~STANDARD REISSUE CAN ONLY BE REVIEWED IF YOU CLICK ON THE LINK TO THE LEFT~~

**IN NO EVENT SHALL IEEE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO: PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE PUBLICATION, USE OF, OR RELIANCE UPON ANY STANDARD, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE AND REGARDLESS OF WHETHER SUCH DAMAGE WAS FORESEEABLE.**

### Translations

The IEEE consensus development process involves the review of documents in English only. In the event that an IEEE standard is translated, only the English version published by IEEE should be considered the approved IEEE standard.

## Official statements

A statement, written or oral, that is not processed in accordance with the IEEE SA Standards Board Operations Manual shall not be considered or inferred to be the official position of IEEE or any of its committees and shall not be considered to be, or be relied upon as, a formal position of IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position of IEEE.

## Comments on standards

Comments for revision of IEEE Standards documents are welcome from any interested party, regardless of membership affiliation with IEEE. However, IEEE does not provide consulting information or advice pertaining to IEEE Standards documents. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Since IEEE standards represent a consensus of concerned interests, it is important that any responses to comments and questions also receive the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to comments or questions except in those cases where the matter has previously been addressed. For the same reason, IEEE does not respond to interpretation requests. Any person who would like to participate in revisions to an IEEE standard is welcome to join the relevant IEEE working group.

Comments on standards should be submitted to the following address:

Secretary, IEEE SA Standards Board

445 Hoes Lane

Piscataway, NJ 08854 USA

## Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the provisions of any IEEE Standards document does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

## Copyrights

IEEE draft and approved standards are copyrighted by IEEE under U.S. and international copyright laws. They are made available by IEEE and are adopted for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making these documents available for use and adoption by public authorities and private users, IEEE does not waive any rights in copyright to the documents.

## Photocopies

Subject to payment of the appropriate fee, IEEE will grant users a limited, non-exclusive license to photocopy portions of any individual standard for company or organizational internal use or individual, non-commercial use only. To arrange for payment of licensing fees, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

## Updating of IEEE Standards documents

Users of IEEE Standards documents should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. A current IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect.

Every IEEE standard is subjected to review at least every ten years. When a document is more than ten years old and has not undergone a revision process, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE standard.

In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit the IEEE SA Website at <https://ieeexplore.ieee.org> or contact IEEE at the address listed previously. For more information about the IEEE SA or IEEE's standards development process, visit the IEEE SA Website at <https://standards.ieee.org>.

## Errata

Errata, if any, for all IEEE standards can be accessed on the IEEE SA Website at the following URL: <https://standards.ieee.org/findstds/errata/index.html>. Users are encouraged to check this URL for errata periodically.

## Patents

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE SA Website at <https://standards.ieee.org/about/sasb/patcom/patents.html>. Letters of Assurance may indicate whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

## Participants

The following individuals were officers and members of the IEEE 802.3 Working Group at the beginning of the IEEE P802.3ca Working Group ballot.

**David J. Law, IEEE 802.3 Working Group Chair**

**Adam Healey, IEEE 802.3 Working Group Vice-Chair**

**Pete Anslow, IEEE 802.3 Working Group Secretary, Phase 1**

**Jon Lewis, IEEE 802.3 Working Group Secretary, Phase 2**

**Steven B. Carlson, IEEE 802.3 Working Group Executive Secretary**

**Valerie Maguire, IEEE 802.3 Working Group Treasurer**

**Curtis Knittle, IEEE P802.3ca Nx25G-EPON Task Force Chair**

**Glen Kramer, IEEE P802.3ca Nx25G-EPON Task Force Vice-Chair**

**Marek Hajduczenia, IEEE P802.3ca Nx25G-EPON Task Force Editor-in-Chief**

John Abbott

David Abramson

Andrea Agnes

Dale Amason

Hongming An

Jes Asmussen

Richard Baca

Tim Baggett

Amrik Bains

Thananya Baldwin

Steven Baumgartner

Denis Beaudoin

Liav Ben-Artzi

Piergiorgio Beruto

Vipul Bhatt

Gao Bo

Martin Bouda

David Brandt

Ralf-Peter Braun

Paul Brooks

Alan Brown

Matthew Brown

Michal Brychta

Gary Burrell

Jairo Bustos Heredia

Adrian Butter

John Calvin

Clark Carty

Craig Chabot

David Chalupsky

Frank Chang

Xin Chang

Golam Choudhury

Keng Hua Chuang

Kamal Dalmia

John D'Ambrosia

Piers Dawe

Fred Dawson

John Deandrea

Gerrit den Besten

Claudio DeSanti

Chris Diminico

Hormoz Djahanshahi

Curtis Donahue

Liang Du

Kathryn Dube

Mike Dudek

Marc Dupuis

Frank Effenberger

David Estes

John Ewen

Borhan Fathi Moghadam

Vincent Ferretti

Brian Franchuk

Matthias Fritsche

Richard Frosch

Shiyong Fu

Mike Gardner

Claude Gauthier

Ali Ghiasi

Joel Goergen

Zhigang Gong

Steven Gorshe

Jens Gottron

Steffen Gruber

Olaf Grau

Robert Grow

Mark Gustlin

Hayden Haynes

Xiang He

Howard Heck

Brian Holden

Rita Horner

Bernd Horrmeyer

Gergely Huszak

Yasuhiro Hyakutake

Jonathan Ingham

Kazuhiko Ishibe

Hideki Isono

Tom Issenhuth

Kenneth Jackson

Andrew Jimenez

John Johnson

Chad Jones

Peter Jones

Lokesh Kabra

Manabu Kagami

Upen Karet

Yasuaki Kawatsu

Yong Kim

Mark Kimber

Jonathan King

Michael Klempa

Elizabeth Kochuparambil

Wojciech Koczwara

Paul Kolesar

Taiji Kondo

Olaf Krieger

Hans Lackner

Jeffrey Lapak

Mark Laubach

Han Hyub Lee

June Hee Lee

Alex Levin

Jon Lewis

David Li

Mike-Peng Li

Jane Lim

Alex Lin

Dekun Liu

Hai-Feng Liu

Karen Liu

Zhenyu Liu

William Lo

Yuchun Lu

Miklos Lukacs

Kent Lusted

Ilya Lyubomirsky

Jeffery Maki

David Malicoat

Flavio Marques

Arthur Marris

Chris Mash

Takeo Masuda

Kirsten Matheus

Erdem Matoglu

Marco Mazzini

Mick McCarthy

Brett McClellan

Larry McMillan

Greg McSorley

Richard Mellitz

STANDARDSPDF.COM : Click to view the PDF of ISO/IEC/IEEE 8802-3:2021/Amd 9:2021

Martin Miller

Toshiyuki Moritake

Thomas Mueller

Edward Nakamoto

Paul Neveux

Gary Nicholl

Shawn Nicholl

John Nolan

Kevin Noll

Mark Nowell

David Ofelt

Josef Ohni

Tom Palkert

Sujan Pandey

Carlos Pardo

Earl Parsons

Gerald Pepper

Phong Pham

David Pielher

Rick Pimpinella

Christopher Pohl

William Powell

Dino Pozzebon

Rick Rabinovich

Zvi Rechtman

Alon Regev

Duane Remein

Victor Renteria

Salvatore Rotolo

Alexander Rysin

Toshiaki Sakai

Hamid Salehi

Sam Sambasivan

Edward Sayre

James Schuessler

Steve Sekel

Masood Shariff

Mizuki Shirao

Jialong Shuai

Jeff Slavick

Daniel Smith

Scott Sommers

Tom Souvignier

Bryan Sparrowhawk

Edward Sprague

Peter Stassar

Heath Stewart

David Stover

Junqing Sun

Liyang Sun

Steve Swanson

Bharat Tailor

Tomoo Takahara

Kohichi Tamura

Mehmet Tazebay

Ronald Tellas

Geoffrey Thompson

Pirooz Tooyserkani

Nathan Tracy

David Tremblay

Stephen Trowbridge

Ta Chin Tseng

Ed Ulrichs

Alexander Umnov

Ricky Vernickel

Marco Vitali

Robert Voss

Dylan Walker

Haifei Wang

Roy Wang

Tongtong Wang

Xinyuan Wang

Xuehuan Wang

Christoph Wechsler

Brian Welch

Matthias Wendt

Natalie Wienckowski

James Withey

Mau-Lin Wu

Peter Wu

Markus Wucher

Dayin Xu

Yu Xu

Shuto Yamamoto

Adrian Young

James Young

Lennart Yseboodt

Andrew Zambell

Conrad Zerna

Richard (Yujia) Zhou

Yan Zhuang

Martin Zielinski

George Zimmerman

Pavel Zivny

Harald Zweck

The following members of the individual balloting committee voted on this standard. Balloters may have voted for approval, disapproval, or abstention.

Thomas Alexander

Nancy Bravin

Matthew Brown

Demetrio Bucaneg, Jr.

Jairo Bustos Heredia

William Byrd

Steven B. Carlson

Juan Carreon

Clark Carty

Pin Chang

Xin Chang

Chan Chen

Joseph Coffey

Charles Cook

John Deandrea

Claudio DeSanti

Vincent Ferretti

Avraham Freedman

Matthias Fritsche

Joel Goergen

Zhigang Gong

Randall Groves

Martin Gubow

Marek Hajduczenia

Adam Healey

Marco Hernandez

David Hess

Werner Hoelzl

Yasuhiro Hyakutake

Raj Jain

SangKwon Jeong

Lokesh Kabra

Stuart Kerry

Yongbum Kim

Curtis Knittle

Glen Kramer

Mark Laubach

David J. Law

Pi-Cheng Law

Han Hyub Lee

Hyeong Ho Lee

David Lewis

Jon Lewis

Karen Liu

Javier Luiso

Valerie Maguire

Jeffery Maki

David Malicoat

Brett McClellan

Richard Mellitz

Tremont Miao

Raymond Nering

Paul Neveux

Paul Nikolich

Satoshi Obara

Thomas Palkert

Carlos Pardo

Bansi Patel

Dev Paul

Arumugam Paventhian

David Pielher

William Powell

R. K. Rannow

Maximilian Riegel

Robert Robinson

Benjamin Rolfe

Dieter Schicketanz

Thomas Starai

Mitsutoshi Sugawara

Ronald Tellas

Geoffrey Thompson

David Tremblay

Mark-Rene Uchida

Dmitri Varsanofiev

George Vlantis

Lisa Ward

Karl Weber

Andreas Wolf

Yu Yuan

Oren Yuen

Zhen Zhou

Pavel Zivny

When the IEEE SA Standards Board approved this standard on 4 June 2020, it had the following membership:

**Gary Hoffman**, *Chair*

**Jon Walter Rosdahl**, *Vice Chair*

**Jean-Philippe Faure**, *Past Chair*

**Konstantinos Karachalios**, *Secretary*

Ted Burse

J. Travis Griffith

Grace Gu

Guido R. Hiertz

Joseph L. Koepfinger\*

John D. Kulick

David J. Law

Howard Li

Dong Liu

Kevin Lu

Paul Nikolich

Damir Novosel

Dorothy Stanley

Mehmet Ulema

Lei Wang

Sha Wei

Philip B. Winston

Daidi Zhong

Jingyi Zhou

\*Member Emeritus

STANDARDSISO.COM : Click to view the full PDF of ISO/IEC/IEEE 8802-3:2021/Amd 9:2021

## Introduction

This introduction is not part of IEEE Std 802.3ca-2020, IEEE Standard for Ethernet. Amendment 9: Physical Layer Specifications and Management Parameters for 25 Gb/s and 50 Gb/s Passive Optical Networks.

IEEE Std 802.3™ was first published in 1985. Since the initial publication, many projects have added functionality or provided maintenance updates to the specifications and text included in the standard. Each IEEE 802.3 project/amendment is identified with a suffix (e.g., IEEE Std 802.3ba™-2010).

The half duplex Media Access Control (MAC) protocol specified in IEEE Std 802.3-1985 is Carrier Sense Multiple Access with Collision Detection (CSMA/CD). This MAC protocol was key to the experimental Ethernet developed at Xerox Palo Alto Research Center, which had a 2.94 Mb/s data rate. Ethernet at 10 Mb/s was jointly released as a public specification by Digital Equipment Corporation (DEC), Intel and Xerox in 1980. Ethernet at 10 Mb/s was approved as an IEEE standard by the IEEE Standards Board in 1983 and subsequently published in 1985 as IEEE Std 802.3-1985. Since 1985, new media options, new speeds of operation, and new capabilities have been added to IEEE Std 802.3. A full duplex MAC protocol was added in 1997.

Some of the major additions to IEEE Std 802.3 are identified in the marketplace with their project number. This is most common for projects adding higher speeds of operation or new protocols. For example, IEEE Std 802.3u™ added 100 Mb/s operation (also called Fast Ethernet), IEEE Std 802.3z added 1000 Mb/s operation (also called Gigabit Ethernet), IEEE Std 802.3ae added 10 Gb/s operation (also called 10 Gigabit Ethernet), IEEE Std 802.3ah™ specified access network Ethernet (also called Ethernet in the First Mile) and IEEE Std 802.3ba added 40 Gb/s operation (also called 40 Gigabit Ethernet) and 100 Gb/s operation (also called 100 Gigabit Ethernet). These major additions are all now included in and are superseded by IEEE Std 802.3-2018 and are not maintained as separate documents.

At the date of IEEE Std 802.3ca-2020 publication, IEEE Std 802.3 was composed of the following documents:

### IEEE Std 802.3-2018

Section One—Includes Clause 1 through Clause 20 and Annex A through Annex H and Annex 4A. Section One includes the specifications for 10 Mb/s operation and the MAC, frame formats and service interfaces used for all speeds of operation.

Section Two—Includes Clause 21 through Clause 33 and Annex 22A through Annex 33E. Section Two includes management attributes for multiple protocols and speed of operation as well as specifications for providing power over twisted pair cabling for multiple operational speeds. It also includes general information on 100 Mb/s operation as well as most of the 100 Mb/s Physical Layer specifications.

Section Three—Includes Clause 34 through Clause 43 and Annex 36A through Annex 43C. Section Three includes general information on 1000 Mb/s operation as well as most of the 1000 Mb/s Physical Layer specifications.

Section Four—Includes Clause 44 through Clause 55 and Annex 44A through Annex 55B. Section Four includes general information on 10 Gb/s operation as well as most of the 10 Gb/s Physical Layer specifications.

Section Five—Includes Clause 56 through Clause 77 and Annex 57A through Annex 76A. Clause 56 through Clause 67 and Clause 75 through Clause 77, as well as associated annexes, specify subscriber access and other Physical Layers and sublayers for operation from 512 kb/s to 10 Gb/s, and defines

services and protocol elements that enable the exchange of IEEE Std 802.3 format frames between stations in a subscriber access network. Clause 68 specifies a 10 Gb/s Physical Layer specification. Clause 69 through Clause 74 and associated annexes specify Ethernet operation over electrical backplanes at speeds of 1000 Mb/s and 10 Gb/s.

Section Six—Includes Clause 78 through Clause 95 and Annex 83A through Annex 93C. Clause 78 specifies Energy-Efficient Ethernet. Clause 79 specifies IEEE 802.3 Organizationally Specific Link Layer Discovery Protocol (LLDP) type, length, and value (TLV) information elements. Clause 80 through Clause 95 and associated annexes include general information on 40 Gb/s and 100 Gb/s operation as well the 40 Gb/s and 100 Gb/s Physical Layer specifications. Clause 90 specifies Ethernet support for time synchronization protocols.

Section Seven—Includes Clause 96 through Clause 115 and Annex 97A through Annex 115A. Clause 96 through Clause 98, Clause 104, and associated annexes, specify Physical Layers and optional features for 100 Mb/s and 1000 Mb/s operation over a single twisted pair. Clause 100 through Clause 103, as well as associated annexes, specify Physical Layers for the operation of the EPON protocol over coaxial distribution networks. Clause 105 through Clause 114 and associated annexes include general information on 25 Gb/s operation as well as 25 Gb/s Physical Layer specifications. Clause 99 specifies a MAC merge sublayer for the interspersing of express traffic. Clause 115 and its associated annex specify a Physical Layer for 1000 Mb/s operation over plastic optical fiber.

Section Eight—Includes Clause 116 through Clause 126 and Annex 119A through Annex 120E. Clause 116 through Clause 124 and associated annexes include general information on 200 Gb/s and 400 Gb/s operation as well the 200 Gb/s and 400 Gb/s Physical Layer specifications. Clause 125 and Clause 126 include general information on 2.5 Gb/s and 5 Gb/s operation as well as 2.5 Gb/s and 5 Gb/s Physical Layer specifications.

#### IEEE Std 802.3cb<sup>TM</sup>-2018

Amendment 1—This amendment includes changes to IEEE Std 802.3-2018 and its amendments, and adds Clause 127 through Clause 130, Annex 127A, Annex 128A, Annex 128B, and Annex 130A. This amendment adds new Physical Layers for operation at 2.5 Gb/s and 5 Gb/s over electrical backplanes.

#### IEEE Std 802.3bt<sup>TM</sup>-2018

Amendment 2—This amendment includes changes to IEEE Std 802.3-2018 and adds Clause 145, Annex 145A, Annex 145B, and Annex 145C. This amendment adds power delivery using all four pairs in the structured wiring plant, resulting in greater power being available to end devices. This amendment also allows for lower standby power consumption in end devices and adds a mechanism to better manage the available power budget.

#### IEEE Std 802.3cd<sup>TM</sup>-2018

Amendment 3—This amendment includes changes to IEEE Std 802.3-2018 and adds Clause 131 through Clause 140 and Annex 135A through Annex 136D. This amendment adds MAC parameters, Physical Layers, and management parameters for the transfer of IEEE 802.3 format frames at 50 Gb/s, 100 Gb/s, and 200 Gb/s.

#### IEEE Std 802.3cn<sup>TM</sup>-2019

Amendment 4—This amendment includes changes to IEEE Std 802.3-2018 and adds 50 Gb/s, 200 Gb/s, and 400 Gb/s Physical Layer specifications and management parameters for operation over single-mode fiber with reaches of at least 40 km.

IEEE Std 802.3cg<sup>TM</sup>-2019

Amendment 5—This amendment includes changes to IEEE Std 802.3-2018 and its amendments and adds Clause 146 through Clause 148 and Annex 146A and Annex 146B. This amendment adds 10 Mb/s Physical Layer specifications and management parameters for operation on a single balanced pair of conductors.

IEEE Std 802.3cq<sup>TM</sup>-2020

Amendment 6—This amendment includes editorial and technical corrections, refinements, and clarifications to Clause 33 and related portions of the standard.

IEEE Std 802.3cm<sup>TM</sup>-2020

Amendment 7—This amendment includes changes to IEEE Std 802.3-2018 and adds Clause 150. This amendment adds Physical Layer (PHY) specifications and management parameters for 400 Gb/s operation on four pairs (400GBASE-SR4.2) and eight pairs (400GBASE-SR8) of multimode fiber, over reaches of at least 100 m.

IEEE Std 802.3ch<sup>TM</sup>-2020

Amendment 8—This amendment includes changes to IEEE Std 802.3-2018 and adds Clause 149, Annex 149A, Annex 149B, and Annex 149C. This amendment adds physical layer specifications and management parameters for operation at 2.5 Gb/s, 5 Gb/s, and 10 Gb/s over a single balanced pair of conductors.

IEEE Std 802.3ca<sup>TM</sup>-2020

Amendment 9—This amendment to IEEE Std 802.3-2018 extends the operation of Ethernet passive optical networks (EPONs) to multiple channels of 25 Gb/s providing both symmetric and asymmetric operation for the following data rates (downstream/upstream): 25/10 Gb/s, 25/25 Gb/s, 50/10 Gb/s, 50/25 Gb/s, and 50/50 Gb/s. This amendment specifies the 25 Gb/s EPON Multi-Channel Reconciliation Sublayer (MCRS), Nx25G-EPON Physical Coding Sublayers (PCSs), Physical Media Attachment (PMA) sublayers, and Physical Medium Dependent (PMD) sublayers that support both symmetric and asymmetric data rates while maintaining backward compatibility with already deployed 10 Gb/s EPON equipment. The EPON operation is defined for distances of at least 20 km, and for a split ratio of at least 1:32.

Two companion documents exist, IEEE Std 802.3.1 and IEEE Std 802.3.2. IEEE Std 802.3.1 describes Ethernet management information base (MIB) modules for use with the Simple Network Management Protocol (SNMP). IEEE Std 802.3.2 describes YANG data models for Ethernet. IEEE Std 802.3.1 and IEEE Std 802.3.2 are updated to add management capability for enhancements to IEEE Std 802.3 after approval of those enhancements.

IEEE Std 802.3 will continue to evolve. New Ethernet capabilities are anticipated to be added within the next few years as amendments to this standard.

## Contents

|                                                                                                    |    |

|----------------------------------------------------------------------------------------------------|----|

| 1. Introduction.....                                                                               | 23 |

| 1.3    Normative references.....                                                                   | 23 |

| 1.4    Definitions .....                                                                           | 23 |

| 1.5    Abbreviations.....                                                                          | 25 |

| 30. Management.....                                                                                | 26 |

| 30.3    Layer management for DTEs.....                                                             | 26 |

| 30.3.2    PHY device managed object class .....                                                    | 26 |

| 30.3.2.1    PHY device attributes.....                                                             | 26 |

| 30.3.2.1.2    aPhyType .....                                                                       | 26 |

| 30.3.2.1.3    aPhyTypeList .....                                                                   | 26 |

| 30.3.5    MPCP managed object class .....                                                          | 27 |

| 30.3.5.1    MPCP Attributes.....                                                                   | 27 |

| 30.3.5.1.2    aMPCPAdminState.....                                                                 | 27 |

| 30.3.5.1.3    aMPCPMode.....                                                                       | 27 |

| 30.3.5.1.4    aMPCPLinkID .....                                                                    | 27 |

| 30.5    Layer management for medium attachment units (MAUs).....                                   | 27 |

| 30.5.1    MAU managed object class.....                                                            | 27 |

| 30.5.1.1    MAU attributes .....                                                                   | 27 |

| 30.5.1.2    aMAUType .....                                                                         | 27 |

| 45. Management Data Input/Output (MDIO) Interface.....                                             | 31 |

| 45.2    MDIO Interface Registers.....                                                              | 31 |

| 45.2.1    PMA/PMD registers.....                                                                   | 31 |

| 45.2.1.23a    PMA/PMD control 3 register (Register 1.29) .....                                     | 31 |

| 45.2.1.23a.1    Downstream differential encoding (1.29.15).....                                    | 31 |

| 45.2.1.23a.2    PMA/PMD type selection (1.29.5:0) .....                                            | 31 |

| 45.2.1.134a    Nx25G-EPON PMA/PMD extended ability register (Registers 1.1000 through 1.1002)..... | 33 |

| 45.2.1.134a.1    25GBASE-PQX-U3 (1.1000.15) .....                                                  | 35 |

| 45.2.1.134a.2    25GBASE-PQX-U2 (1.1000.14).....                                                   | 35 |

| 45.2.1.134a.3    25GBASE-PQX-D3 (1.1000.13) .....                                                  | 35 |

| 45.2.1.134a.4    25GBASE-PQX-D2 (1.1000.12) .....                                                  | 35 |

| 45.2.1.134a.5    25GBASE-PQG-U3 (1.1000.11) .....                                                  | 35 |

| 45.2.1.134a.6    25GBASE-PQG-U2 (1.1000.10) .....                                                  | 35 |

| 45.2.1.134a.7    25GBASE-PQG-D3 (1.1000.9) .....                                                   | 36 |

| 45.2.1.134a.8    25GBASE-PQG-D2 (1.1000.8) .....                                                   | 36 |

| 45.2.1.134a.9    25/10GBASE-PQX-U3 (1.1000.7) .....                                                | 36 |

| 45.2.1.134a.10    25/10GBASE-PQX-U2 (1.1000.6) .....                                               | 36 |

| 45.2.1.134a.11    25/10GBASE-PQX-D3 (1.1000.5) .....                                               | 36 |

| 45.2.1.134a.12    25/10GBASE-PQX-D2 (1.1000.4) .....                                               | 36 |

| 45.2.1.134a.13    25/10GBASE-PQG-U3 (1.1000.3) .....                                               | 36 |

| 45.2.1.134a.14    25/10GBASE-PQG-U2 (1.1000.2) .....                                               | 36 |

| 45.2.1.134a.15    25/10GBASE-PQG-D3 (1.1000.1) .....                                               | 36 |

| 45.2.1.134a.16    25/10GBASE-PQG-D2 (1.1000.0) .....                                               | 37 |

| 45.2.1.134a.17    50/25GBASE-PQX-U3 (1.1001.15) .....                                              | 37 |

| 45.2.1.134a.18    50/25GBASE-PQX-U2 (1.1001.14) .....                                              | 37 |

| 45.2.1.134a.19    50/25GBASE-PQX-D3 (1.1001.13) .....                                              | 37 |

|                |                                                                                                                  |    |

|----------------|------------------------------------------------------------------------------------------------------------------|----|

| 45.2.1.134a.20 | 50/25GBASE-PQX-D2 (1.1001.12) .....                                                                              | 37 |

| 45.2.1.134a.21 | 50/25GBASE-PQG-U3 (1.1001.11) .....                                                                              | 37 |

| 45.2.1.134a.22 | 50/25GBASE-PQG-U2 (1.1001.10) .....                                                                              | 37 |

| 45.2.1.134a.23 | 50/25GBASE-PQG-D3 (1.1001.9) .....                                                                               | 37 |

| 45.2.1.134a.24 | 50/25GBASE-PQG-D2 (1.1001.8) .....                                                                               | 37 |

| 45.2.1.134a.25 | 50/10GBASE-PQX-U3 (1.1001.7) .....                                                                               | 38 |

| 45.2.1.134a.26 | 50/10GBASE-PQX-U2 (1.1001.6) .....                                                                               | 38 |

| 45.2.1.134a.27 | 50/10GBASE-PQX-D3 (1.1001.5) .....                                                                               | 38 |

| 45.2.1.134a.28 | 50/10GBASE-PQX-D2 (1.1001.4) .....                                                                               | 38 |

| 45.2.1.134a.29 | 50/10GBASE-PQG-U3 (1.1001.3) .....                                                                               | 38 |

| 45.2.1.134a.30 | 50/10GBASE-PQG-U2 (1.1001.2) .....                                                                               | 38 |

| 45.2.1.134a.31 | 50/10GBASE-PQG-D3 (1.1001.1) .....                                                                               | 38 |

| 45.2.1.134a.32 | 50/10GBASE-PQG-D2 (1.1001.0) .....                                                                               | 38 |

| 45.2.1.134a.33 | 50GBASE-PQX-U3 (1.1002.7) .....                                                                                  | 38 |

| 45.2.1.134a.34 | 50GBASE-PQX-U2 (1.1002.6) .....                                                                                  | 39 |

| 45.2.1.134a.35 | 50GBASE-PQX-D3 (1.1002.5) .....                                                                                  | 39 |

| 45.2.1.134a.36 | 50GBASE-PQX-D2 (1.1002.4) .....                                                                                  | 39 |

| 45.2.1.134a.37 | 50GBASE-PQG-U3 (1.1002.3) .....                                                                                  | 39 |

| 45.2.1.134a.38 | 50GBASE-PQG-U2 (1.1002.2) .....                                                                                  | 39 |

| 45.2.1.134a.39 | 50GBASE-PQG-D3 (1.1002.1) .....                                                                                  | 39 |

| 45.2.1.134a.40 | 50GBASE-PQG-D2 (1.1002.0) .....                                                                                  | 39 |

| 45.2.3         | PCS registers .....                                                                                              | 40 |

| 45.2.3.1       | PCS control 1 register (Register 3.0).....                                                                       | 40 |

| 45.2.3.6       | PCS control 2 register (Register 3.7).....                                                                       | 41 |

| 45.2.3.6.1     | PCS type selection (3.7.34:0).....                                                                               | 41 |

| 45.2.3.8       | PCS status 3 register (Register 3.9).....                                                                        | 41 |

| 45.2.3.8.aa    | 25GBASE-PQ capable (3.9.7).....                                                                                  | 42 |

| 45.2.3.8.ab    | 25/10GBASE-PQ capable (3.9.6).....                                                                               | 42 |

| 45.2.3.8.ac    | 25GBASE-PQ Rx only capable (3.9.5).....                                                                          | 42 |

| 45.2.3.8.ad    | 25GBASE-PQ Tx only capable (3.9.4).....                                                                          | 42 |

| 45.2.3.41      | 10/1GBASE-PRX and 10GBASE-PR10G-EPON and Nx25G-EPON corrected FEC codewords counter (Register 3.76, 3.77).....   | 42 |

| 45.2.3.42      | 10/1GBASE-PRX and 10GBASE-PR10G-EPON and Nx25G-EPON uncorrected FEC codewords counter (Register 3.78, 3.79)..... | 43 |

| 45.2.3.43      | 10GBASE-PR and, 10/1GBASE-PRX, and Nx25G-EPON BER monitor interval timer control register (Register 3.80) .....  | 43 |

| 45.2.3.44      | 10GBASE-PR and, 10/1GBASE-PRX, and Nx25G-EPON BER monitor status (Register 3.81) .....                           | 44 |

| 45.2.3.44.1    | 10GBASE-PR and, 10/1GBASE-PRX, and Nx25G-EPON PCS high BER (3.81.0) .....                                        | 44 |

| 45.2.3.44.2    | 10GBASE-PR and, 10/1GBASE-PRX, and Nx25G-EPON PCS latched high BER (3.81.1) .....                                | 45 |

| 45.2.3.45      | 10GBASE-PR and, 10/1GBASE-PRX, and Nx25G-EPON BER monitor threshold control (Register 3.82) .....                | 45 |

| 45.2.3.45a     | Nx25G-EPON synchronization pattern registers (Registers 3.83 through 3.134).....                                 | 45 |

| 45.2.3.45a.1   | SP3 bit 257 (3.83.5) .....                                                                                       | 46 |

| 45.2.3.45a.2   | SP3 balanced (3.83.4) .....                                                                                      | 46 |

| 45.2.3.45a.3   | SP2 bit 257 (3.83.3) .....                                                                                       | 46 |

| 45.2.3.45a.4   | SP2 balanced (3.83.2) .....                                                                                      | 46 |

| 45.2.3.45a.5   | SP1 bit 257 (3.83.1) .....                                                                                       | 47 |

| 45.2.3.45a.6   | SP1 balanced (3.83.0) .....                                                                                      | 47 |

| 45.2.3.45a.7   | SP1 pattern (3.84.0 through 3.99.15) .....                                                                       | 47 |

| 45.2.3.45a.8   | SP1 length (3.100.15:0) .....                                                                                    | 47 |

STANDARDSISO.COM CHECKER PDF OF ISO/IEC/IEEE 8802-3:2021/Amd.9:2021

|               |                                                                                                                                     |    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 45.2.3.45a.9  | SP2 pattern (3.101.0 through 3.116.15).....                                                                                         | 47 |

| 45.2.3.45a.10 | SP2 length (3.117.15:0) .....                                                                                                       | 47 |

| 45.2.3.45a.11 | SP3 pattern (3.118.0 through 3.133.15).....                                                                                         | 47 |

| 45.2.3.45a.12 | SP3 length (3.134.15:0) .....                                                                                                       | 47 |

| 45.5          | Protocol implementation conformance statement (PICS) proforma for Clause 45,<br>Management Data Input/Output (MDIO) interface ..... | 48 |

| 45.5.1        | Introduction .....                                                                                                                  | 48 |

| 45.5.2        | Identification .....                                                                                                                | 48 |

| 45.5.2.1      | Implementation identification.....                                                                                                  | 48 |

| 45.5.2.2      | Protocol summary .....                                                                                                              | 48 |

| 45.5.3        | PICS proforma tables for the Management Data Input Output (MDIO) interface .....                                                    | 49 |

| 45.5.3.3      | PMA/PMD management functions .....                                                                                                  | 49 |

| 45.5.3.7      | PCS management functions.....                                                                                                       | 49 |

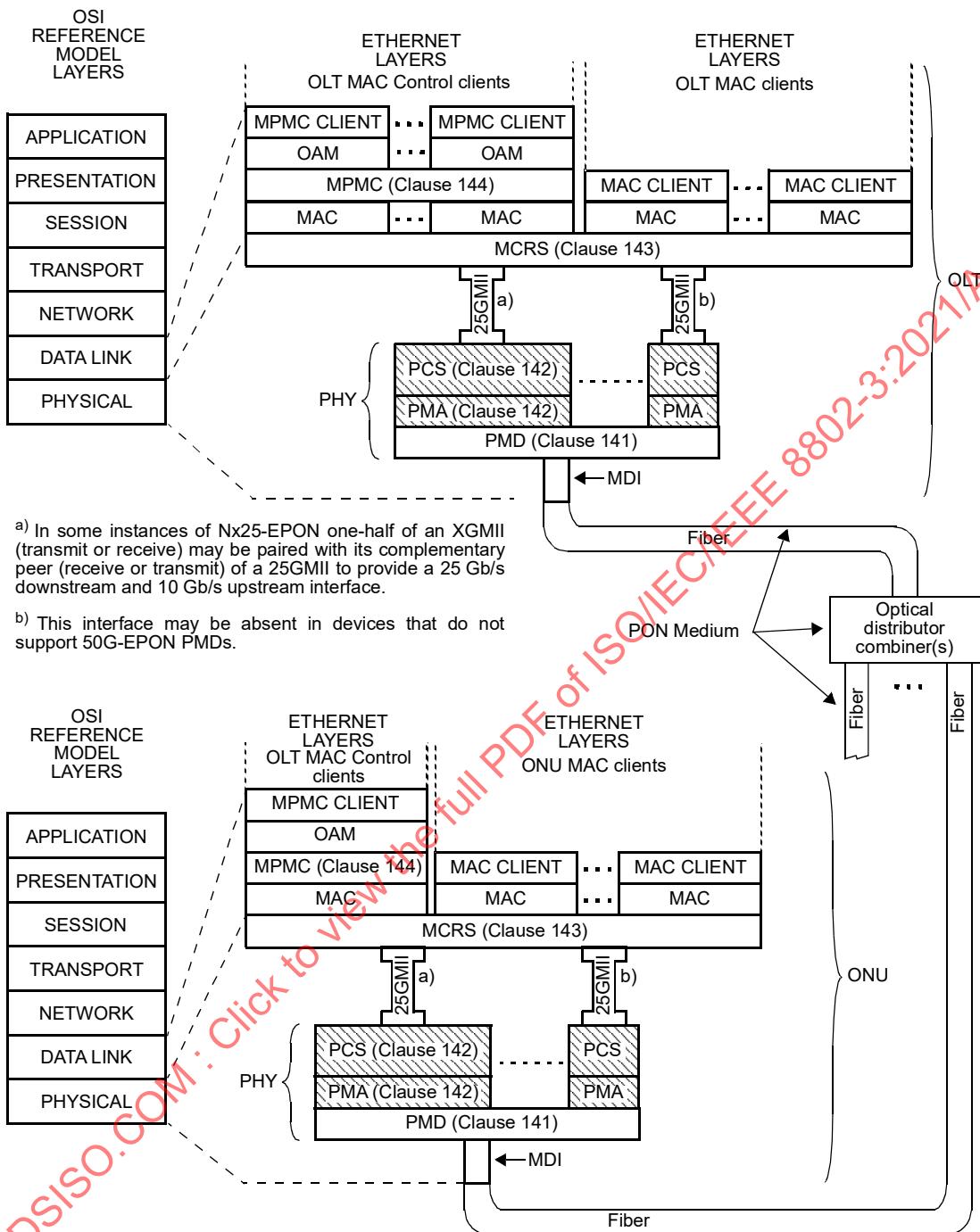

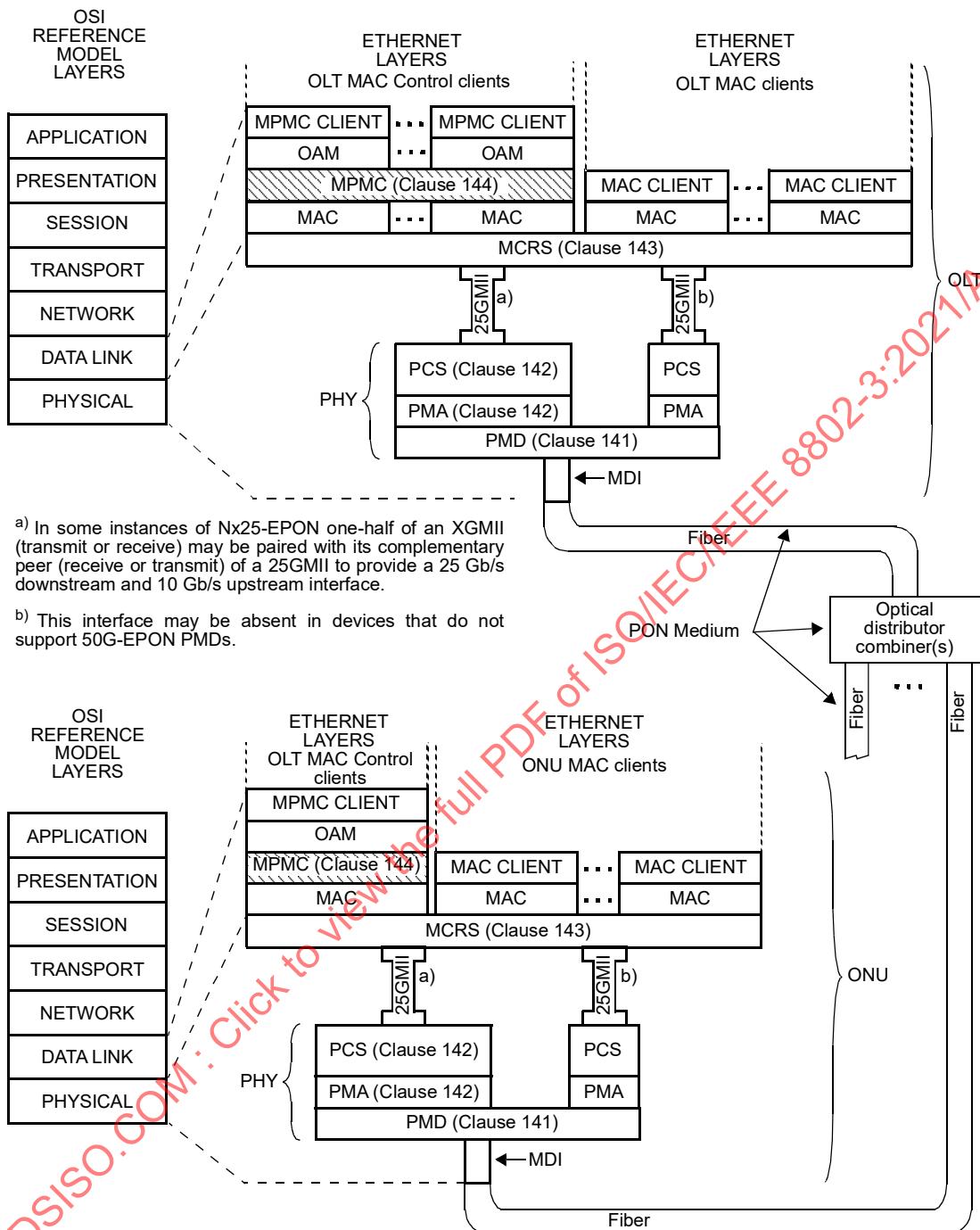

| 56.           | Introduction to Ethernet for subscriber access networks .....                                                                       | 50 |

| 56.1          | Overview.....                                                                                                                       | 50 |

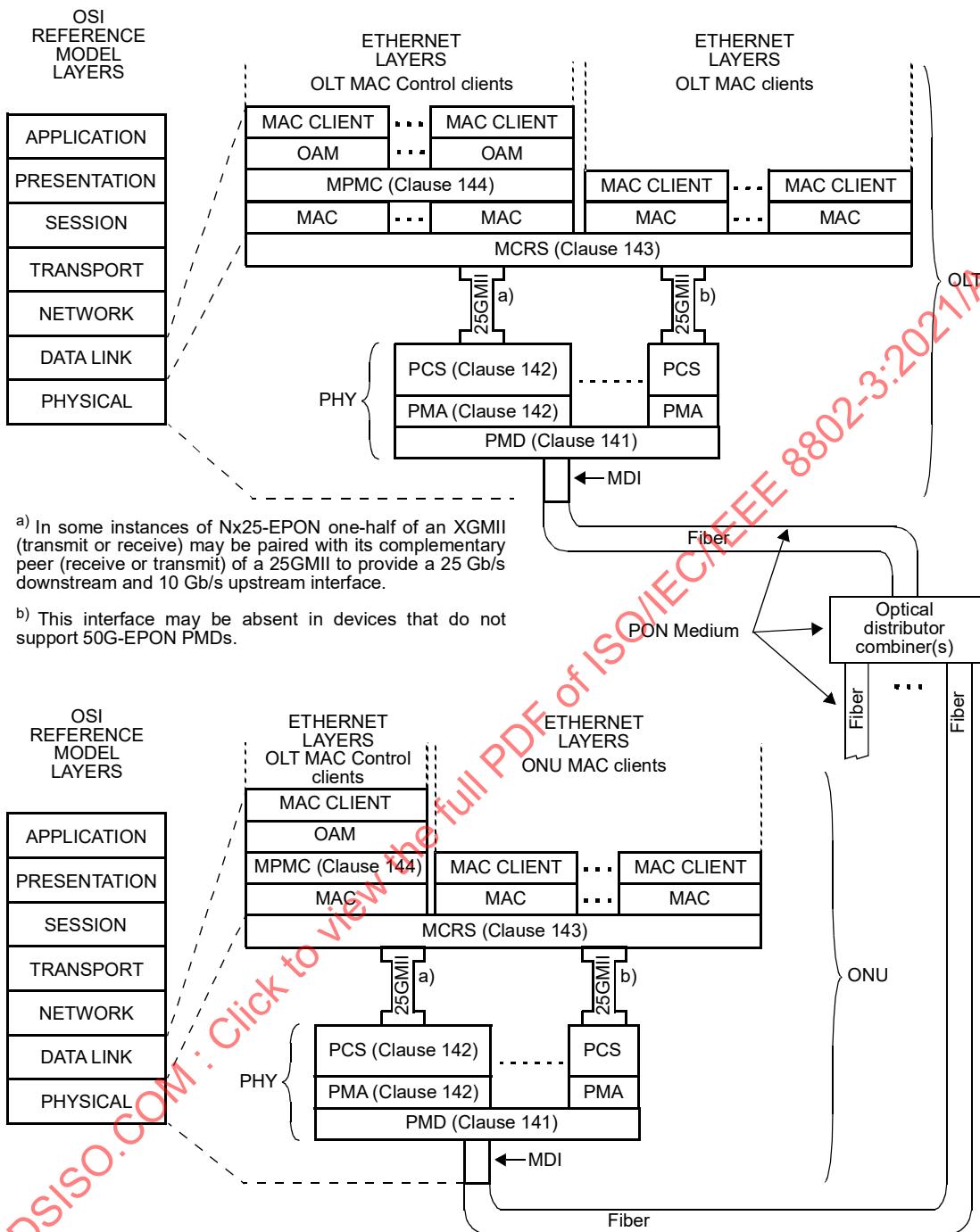

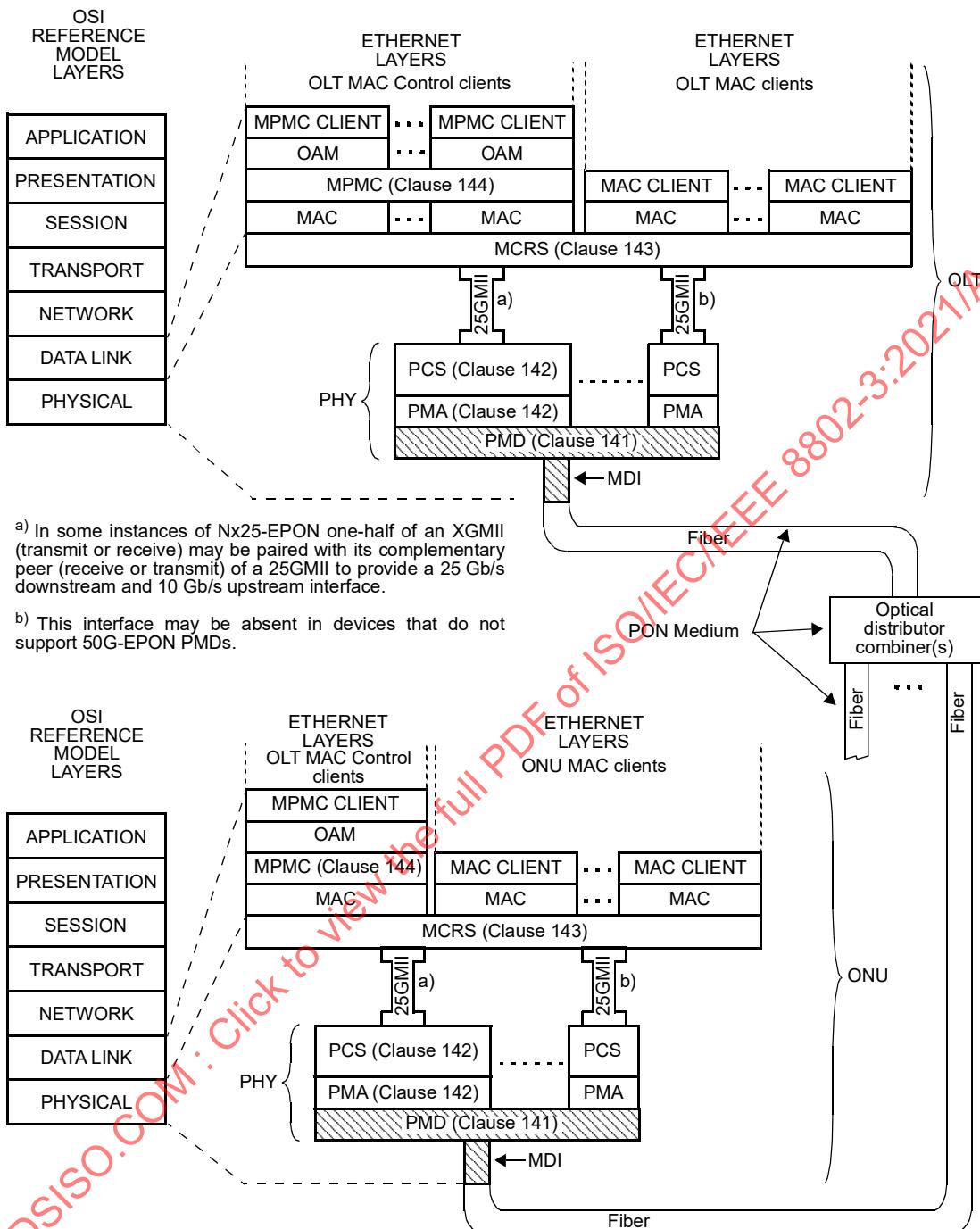

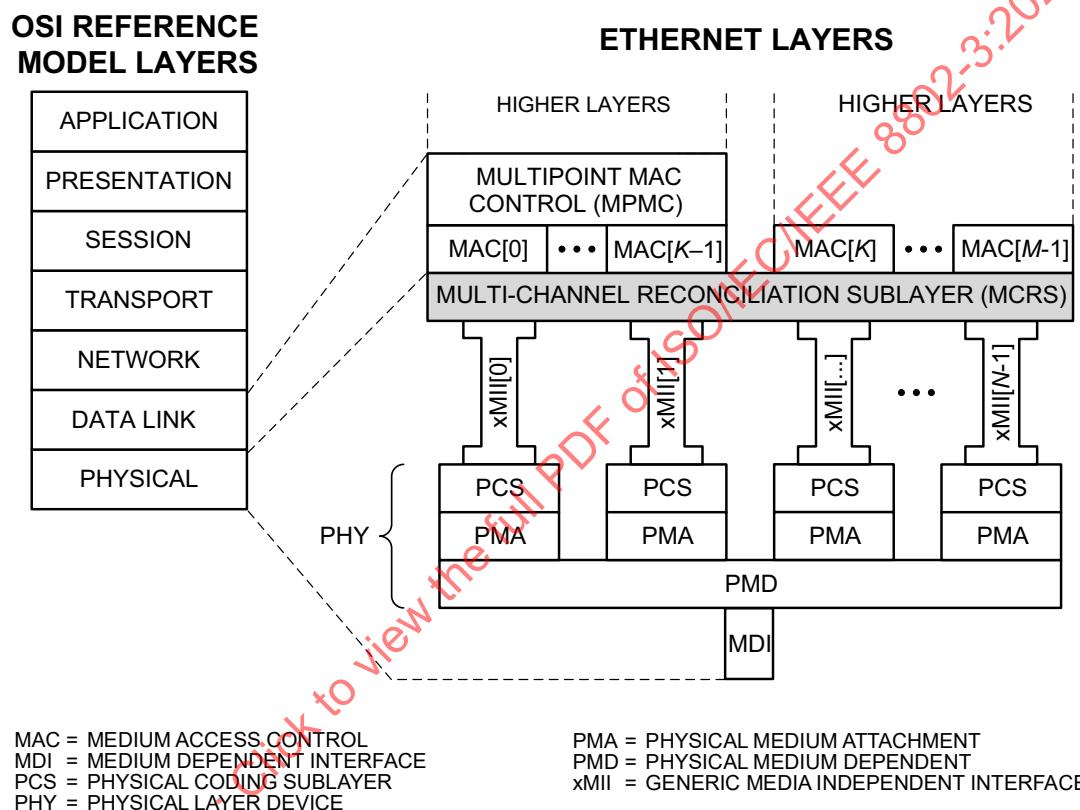

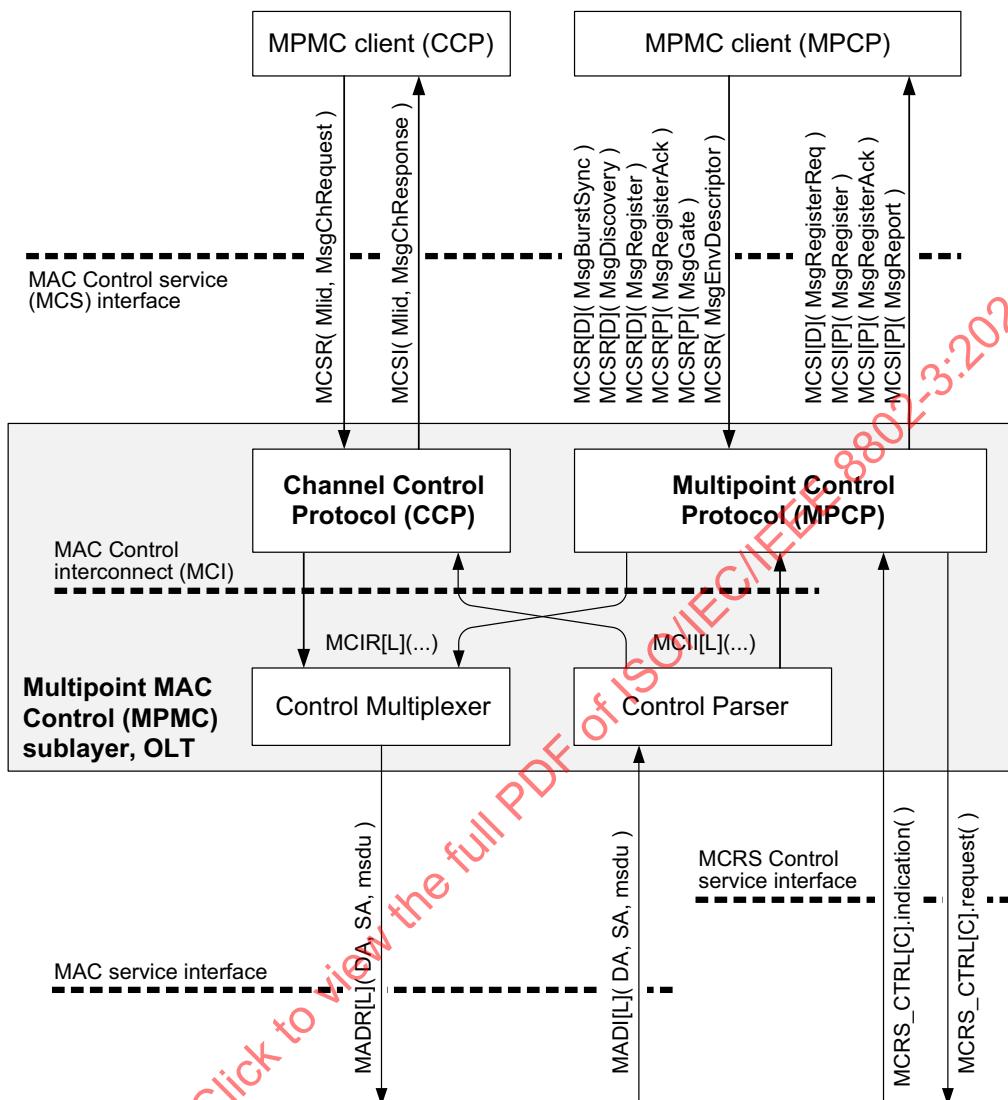

| 56.1.2        | Summary of P2MP sublayers.....                                                                                                      | 50 |

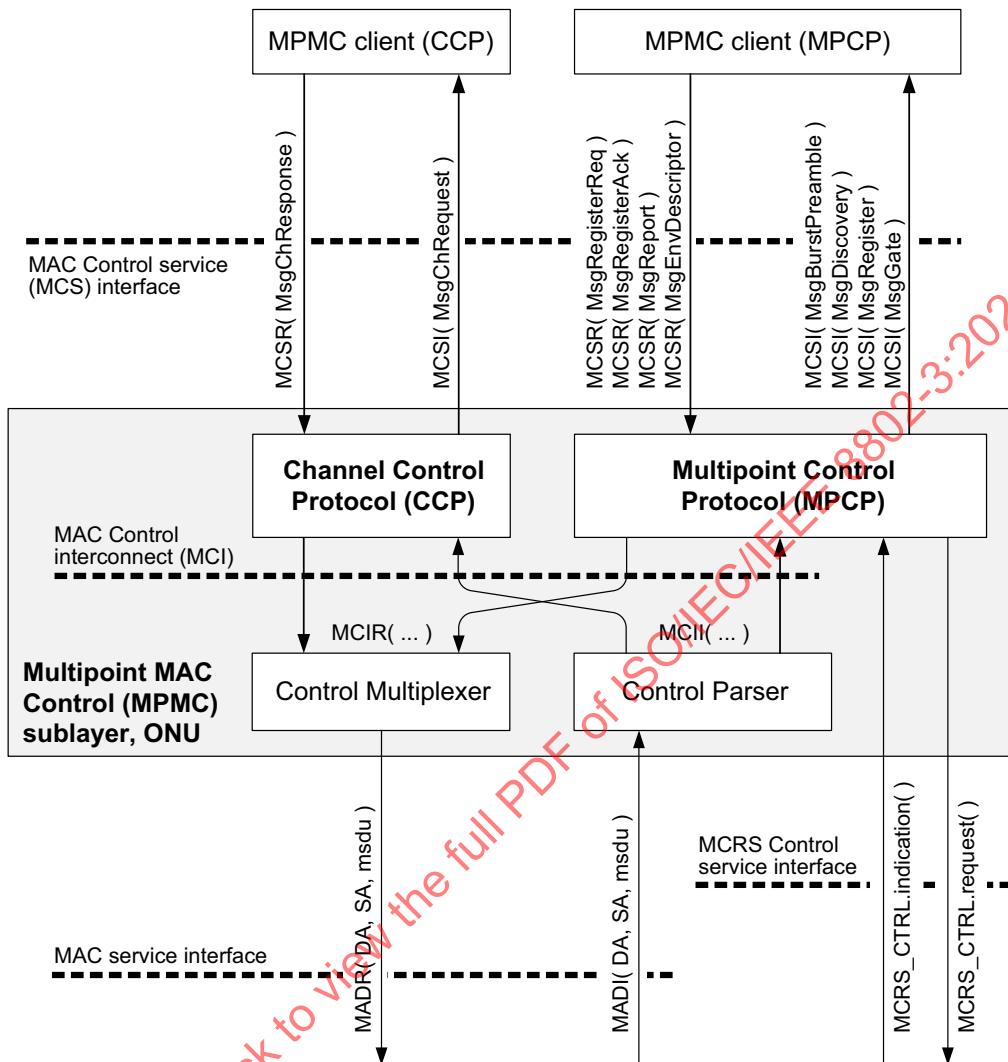

| 56.1.2.1      | Multipoint MAC Control Protocol (MPCP).....                                                                                         | 52 |

| 56.1.2.2      | Reconciliation Sublayer (RS) and media independent interfaces .....                                                                 | 52 |

| 56.1.3        | Physical Layer signaling systems.....                                                                                               | 52 |

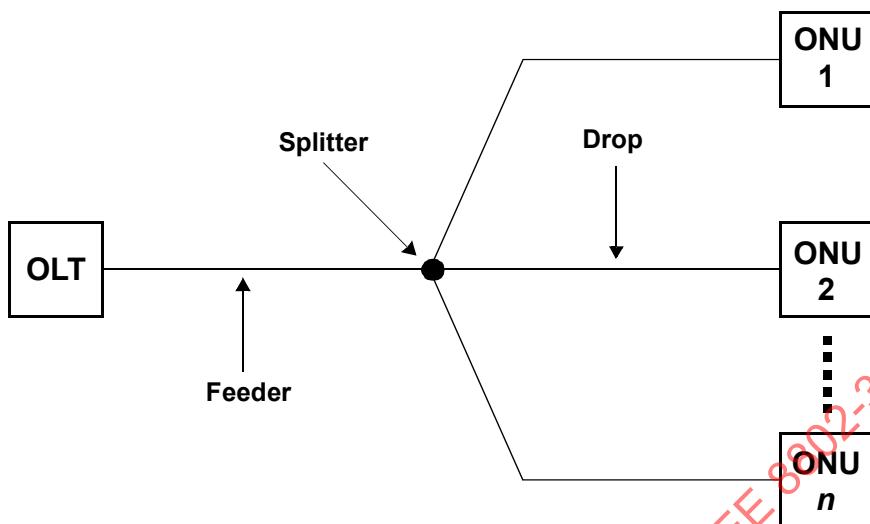

| 67.           | System considerations for Ethernet subscriber access networks .....                                                                 | 59 |

| 67.1          | Overview.....                                                                                                                       | 59 |

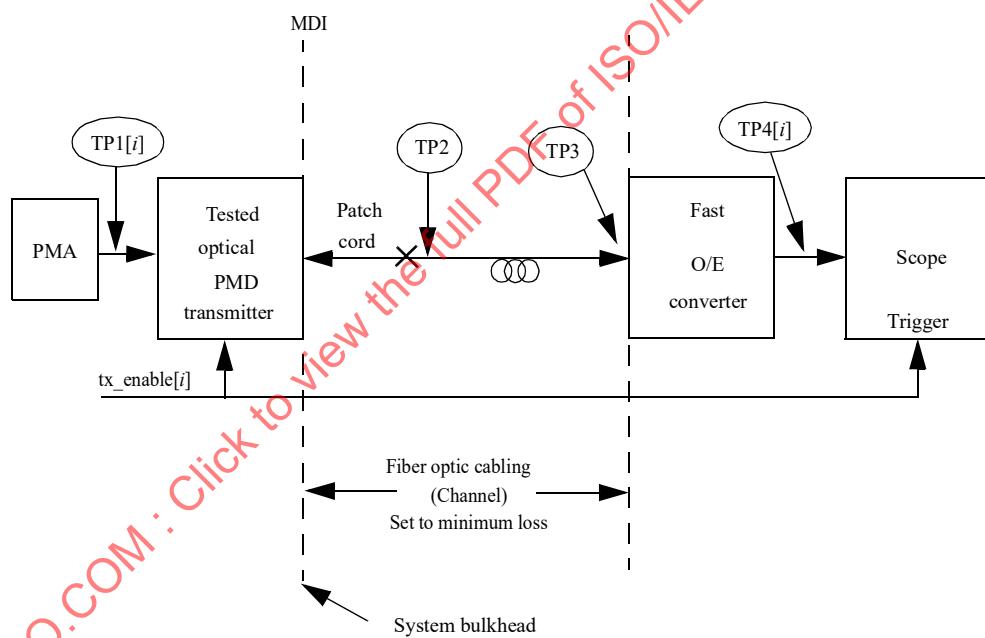

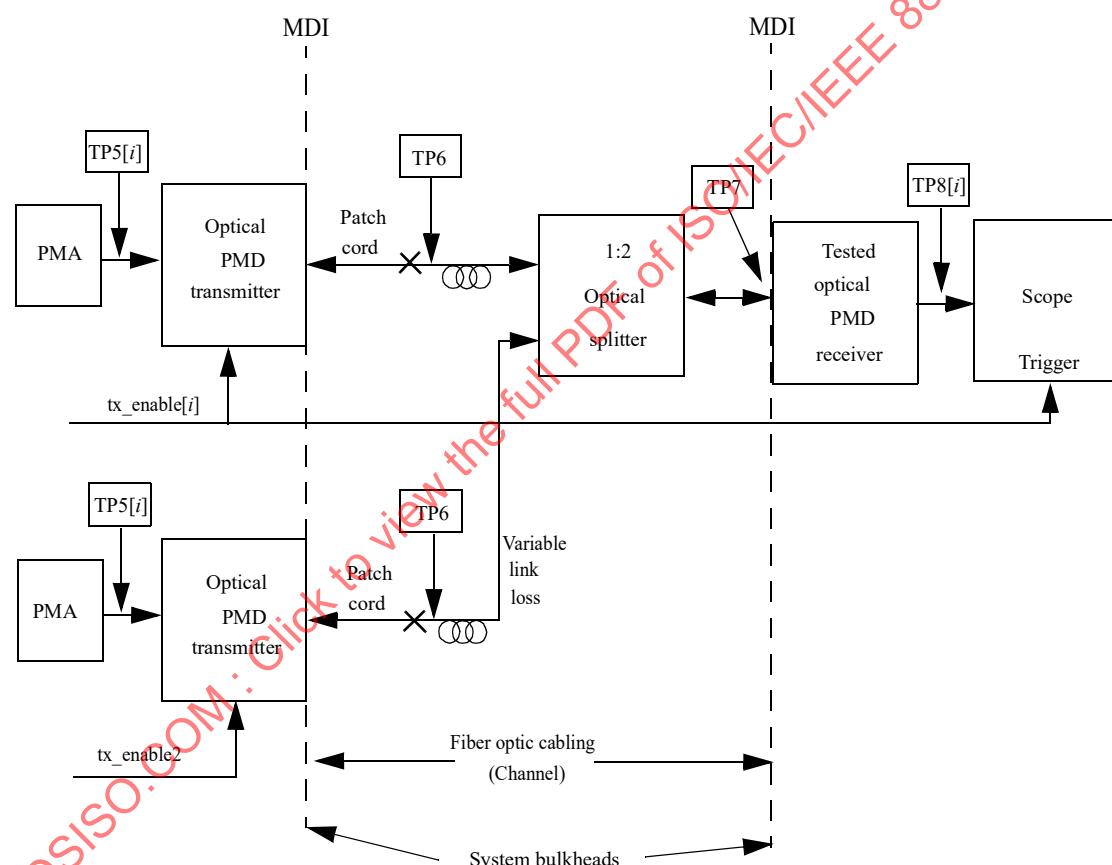

| 141.          | Physical Medium Dependent (PMD) sublayer and medium for Nx25G-EPON passive optical<br>networks.....                                 | 61 |

| 141.1         | Overview.....                                                                                                                       | 61 |

| 141.1.1       | Terminology.....                                                                                                                    | 61 |

| 141.1.2       | Positioning of the PMD sublayer within the IEEE 802.3 architecture.....                                                             | 61 |

| 141.1.3       | PHY link types .....                                                                                                                | 61 |

| 141.2         | PMD nomenclature .....                                                                                                              | 64 |

| 141.2.1       | Introduction .....                                                                                                                  | 64 |

| 141.2.2       | PMD rate classes .....                                                                                                              | 64 |

| 141.2.3       | PMD coexistence classes .....                                                                                                       | 64 |

| 141.2.4       | PMD transmission direction classes.....                                                                                             | 64 |

| 141.2.5       | PMD power classes .....                                                                                                             | 64 |

| 141.2.6       | PMD naming .....                                                                                                                    | 65 |

| 141.2.7       | Supported combinations of OLT and ONU PMDs .....                                                                                    | 65 |

| 141.2.7.1     | PHY Links supporting medium power budget.....                                                                                       | 66 |

| 141.2.7.2     | PHY Links supporting high power budget .....                                                                                        | 67 |

| 141.3         | PMD functional specifications.....                                                                                                  | 67 |

| 141.3.1       | PMD service interface .....                                                                                                         | 67 |

| 141.3.1.1     | Channel-to-wavelength mapping.....                                                                                                  | 67 |

| 141.3.1.2     | Delay constraints .....                                                                                                             | 68 |

| 141.3.1.3     | PMD_UNITDATA[i].request.....                                                                                                        | 68 |

| 141.3.1.4     | PMD_UNITDATA[i].indication .....                                                                                                    | 68 |

| 141.3.1.5     | PMD_SIGNAL[i].request.....                                                                                                          | 69 |

| 141.3.1.6     | PMD_SIGNAL[i].indication .....                                                                                                      | 69 |

| 141.3.2       | PMD block diagram .....                                                                                                             | 69 |

| 141.3.3       | PMD transmit function .....                                                                                                         | 70 |

| 141.3.4       | PMD receive function .....                                                                                                          | 70 |

|            |                                                                                                                                                                                 |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 141.3.5    | PMD signal detect function.....                                                                                                                                                 | 70 |

| 141.3.5.1  | ONU PMD signal detect.....                                                                                                                                                      | 70 |

| 141.3.5.2  | OLT PMD signal detect.....                                                                                                                                                      | 71 |

| 141.3.5.3  | Nx25G-EPON signal detect functions.....                                                                                                                                         | 71 |

| 141.4      | Wavelength allocation .....                                                                                                                                                     | 71 |

| 141.5      | PMD to MDI optical specifications for OLT PMDs .....                                                                                                                            | 72 |

| 141.5.1    | Transmitter optical specifications .....                                                                                                                                        | 72 |

| 141.5.2    | Receiver optical specifications.....                                                                                                                                            | 72 |

| 141.6      | PMD to MDI optical specifications for ONU PMDs .....                                                                                                                            | 77 |

| 141.6.1    | Transmitter optical specifications .....                                                                                                                                        | 77 |

| 141.6.2    | Receiver optical specifications.....                                                                                                                                            | 80 |

| 141.7      | Definitions of optical parameters and measurement methods .....                                                                                                                 | 82 |

| 141.7.1    | Insertion loss .....                                                                                                                                                            | 82 |

| 141.7.2    | Test patterns .....                                                                                                                                                             | 82 |

| 141.7.3    | Wavelength and spectral width measurement.....                                                                                                                                  | 82 |

| 141.7.4    | Optical power measurements .....                                                                                                                                                | 82 |

| 141.7.5    | Extinction ratio measurements .....                                                                                                                                             | 82 |

| 141.7.6    | Optical Modulation Amplitude (OMA) test procedure.....                                                                                                                          | 82 |

| 141.7.7    | Relative intensity noise optical modulation amplitude (RINxOMA) measuring procedure.....                                                                                        | 82 |

| 141.7.8    | Transmit optical waveform (transmit eye).....                                                                                                                                   | 83 |

| 141.7.9    | Transmitter and dispersion penalty (TDP) for 25G .....                                                                                                                          | 83 |

| 141.7.9.1  | Reference transmitter requirements.....                                                                                                                                         | 83 |

| 141.7.9.2  | Channel requirements .....                                                                                                                                                      | 83 |

| 141.7.9.3  | Reference receiver requirements .....                                                                                                                                           | 83 |

| 141.7.9.4  | Test procedure .....                                                                                                                                                            | 83 |

| 141.7.10   | Receive sensitivity.....                                                                                                                                                        | 84 |

| 141.7.11   | Stressed receiver conformance test .....                                                                                                                                        | 84 |

| 141.7.12   | Jitter measurements .....                                                                                                                                                       | 84 |

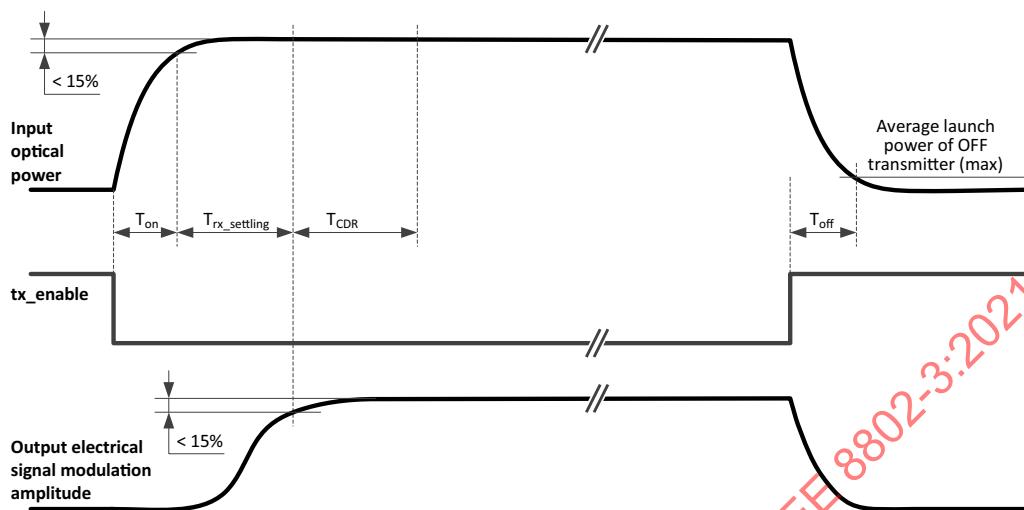

| 141.7.13   | Laser on/off timing measurement .....                                                                                                                                           | 84 |

| 141.7.13.1 | Definitions .....                                                                                                                                                               | 84 |

| 141.7.13.2 | Test specification.....                                                                                                                                                         | 84 |

| 141.7.14   | Receiver settling timing measurement .....                                                                                                                                      | 86 |

| 141.7.14.1 | Definitions .....                                                                                                                                                               | 86 |

| 141.7.14.2 | Test specification.....                                                                                                                                                         | 86 |

| 141.8      | Environmental, safety, and labeling .....                                                                                                                                       | 87 |

| 141.8.1    | General safety.....                                                                                                                                                             | 87 |

| 141.8.2    | Laser safety .....                                                                                                                                                              | 87 |

| 141.8.3    | Installation.....                                                                                                                                                               | 87 |

| 141.8.4    | Environment.....                                                                                                                                                                | 87 |

| 141.8.5    | PMD labeling .....                                                                                                                                                              | 87 |

| 141.9      | Characteristics of the fiber optic cabling .....                                                                                                                                | 88 |

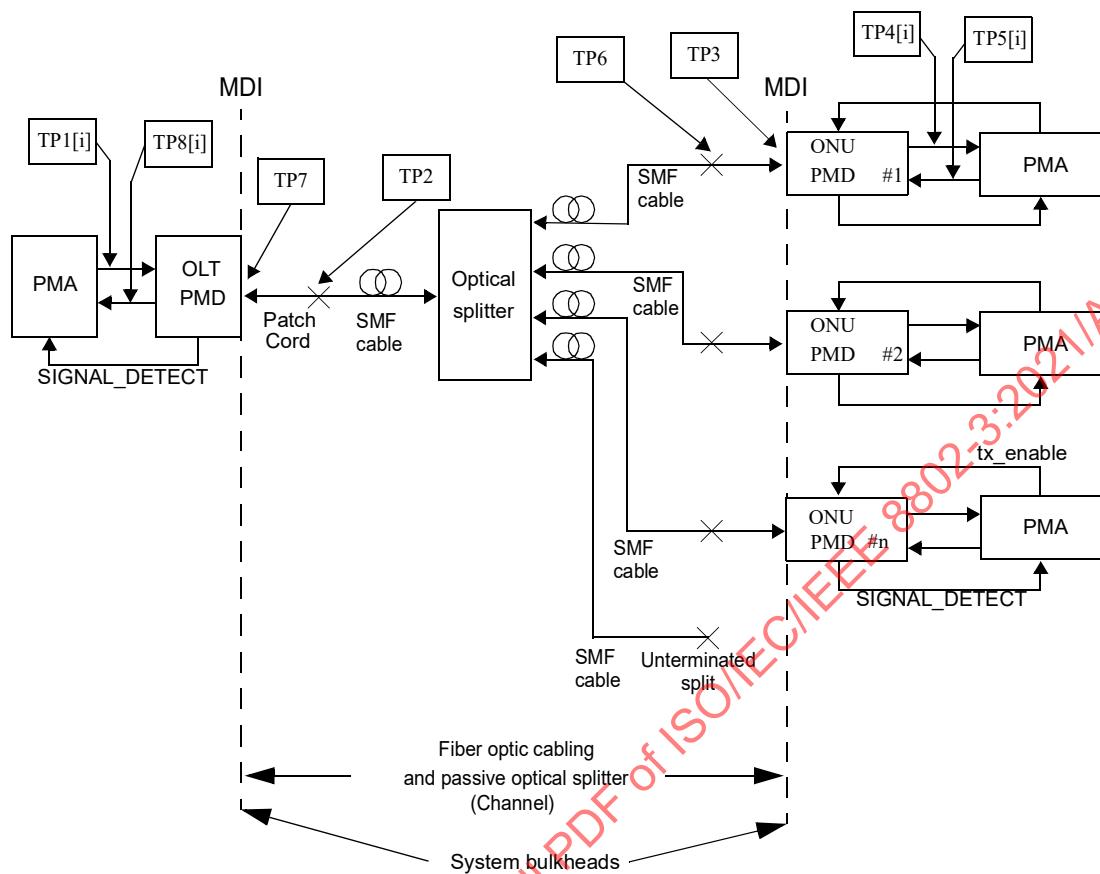

| 141.9.1    | Fiber optic cabling model.....                                                                                                                                                  | 88 |

| 141.9.2    | Optical fiber and cable .....                                                                                                                                                   | 88 |

| 141.9.3    | Optical fiber connection .....                                                                                                                                                  | 88 |

| 141.9.4    | Medium Dependent Interface (MDI) .....                                                                                                                                          | 89 |

| 141.10     | Protocol implementation conformance statement (PICS) proforma for Clause 141, Physical Medium Dependent (PMD) sublayer and medium for Nx25G-EPON passive optical networks ..... | 90 |

| 141.10.1   | Introduction .....                                                                                                                                                              | 90 |

| 141.10.2   | Identification .....                                                                                                                                                            | 90 |

| 141.10.2.1 | Implementation identification.....                                                                                                                                              | 90 |

| 141.10.2.2 | Protocol summary .....                                                                                                                                                          | 90 |

| 141.10.3   | Major capabilities/options .....                                                                                                                                                | 91 |

|             |                                                                                                                                                                                               |     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 141.10.4    | PICS proforma tables for Physical Medium Dependent (PMD) sublayer and medium for passive optical networks, type 25/10GBASE-PQ, 25GBASE-PQ, 50/10GBASE-PQ, 50/25GBASE-PQ, and 50GBASE-PQ ..... | 94  |

| 141.10.4.1  | PMD functional specifications .....                                                                                                                                                           | 94  |

| 141.10.4.2  | PMD to MDI optical specifications for 25/10GBASE-PQG-D2 .....                                                                                                                                 | 95  |

| 141.10.4.3  | PMD to MDI optical specifications for 25/10GBASE-PQG-D3 .....                                                                                                                                 | 95  |

| 141.10.4.4  | PMD to MDI optical specifications for 25/10GBASE-PQX-D2 .....                                                                                                                                 | 95  |

| 141.10.4.5  | PMD to MDI optical specifications for 25/10GBASE-PQX-D3 .....                                                                                                                                 | 96  |

| 141.10.4.6  | PMD to MDI optical specifications for 25GBASE-PQG-D2 .....                                                                                                                                    | 96  |

| 141.10.4.7  | PMD to MDI optical specifications for 25GBASE-PQG-D3 .....                                                                                                                                    | 96  |

| 141.10.4.8  | PMD to MDI optical specifications for 25GBASE-PQX-D2 .....                                                                                                                                    | 96  |

| 141.10.4.9  | PMD to MDI optical specifications for 25GBASE-PQX-D3 .....                                                                                                                                    | 97  |

| 141.10.4.10 | PMD to MDI optical specifications for 50/10GBASE-PQG-D2 .....                                                                                                                                 | 97  |

| 141.10.4.11 | PMD to MDI optical specifications for 50/10GBASE-PQG-D3 .....                                                                                                                                 | 97  |

| 141.10.4.12 | PMD to MDI optical specifications for 50/10GBASE-PQX-D2 .....                                                                                                                                 | 97  |

| 141.10.4.13 | PMD to MDI optical specifications for 50/10GBASE-PQX-D3 .....                                                                                                                                 | 98  |

| 141.10.4.14 | PMD to MDI optical specifications for 50/25GBASE-PQG-D2 .....                                                                                                                                 | 98  |

| 141.10.4.15 | PMD to MDI optical specifications for 50/25GBASE-PQG-D3 .....                                                                                                                                 | 98  |

| 141.10.4.16 | PMD to MDI optical specifications for 50/25GBASE-PQX-D2 .....                                                                                                                                 | 98  |

| 141.10.4.17 | PMD to MDI optical specifications for 50/25GBASE-PQX-D3 .....                                                                                                                                 | 99  |

| 141.10.4.18 | PMD to MDI optical specifications for 50GBASE-PQG-D2 .....                                                                                                                                    | 99  |

| 141.10.4.19 | PMD to MDI optical specifications for 50GBASE-PQG-D3 .....                                                                                                                                    | 99  |

| 141.10.4.20 | PMD to MDI optical specifications for 50GBASE-PQX-D2 .....                                                                                                                                    | 99  |

| 141.10.4.21 | PMD to MDI optical specifications for 50GBASE-PQX-D3 .....                                                                                                                                    | 100 |

| 141.10.4.22 | PMD to MDI optical specifications for 25/10GBASE-PQG-U2 .....                                                                                                                                 | 100 |

| 141.10.4.23 | PMD to MDI optical specifications for 25/10GBASE-PQG-U3 .....                                                                                                                                 | 100 |

| 141.10.4.24 | PMD to MDI optical specifications for 25/10GBASE-PQX-U2 .....                                                                                                                                 | 100 |

| 141.10.4.25 | PMD to MDI optical specifications for 25/10GBASE-PQX-U3 .....                                                                                                                                 | 101 |

| 141.10.4.26 | PMD to MDI optical specifications for 25GBASE-PQG-U2 .....                                                                                                                                    | 101 |

| 141.10.4.27 | PMD to MDI optical specifications for 25GBASE-PQG-U3 .....                                                                                                                                    | 101 |

| 141.10.4.28 | PMD to MDI optical specifications for 25GBASE-PQX-U2 .....                                                                                                                                    | 101 |

| 141.10.4.29 | PMD to MDI optical specifications for 25GBASE-PQX-U3 .....                                                                                                                                    | 102 |

| 141.10.4.30 | PMD to MDI optical specifications for 50/10GBASE-PQG-U2 .....                                                                                                                                 | 102 |

| 141.10.4.31 | PMD to MDI optical specifications for 50/10GBASE-PQG-U3 .....                                                                                                                                 | 102 |

| 141.10.4.32 | PMD to MDI optical specifications for 50/10GBASE-PQX-U2 .....                                                                                                                                 | 102 |

| 141.10.4.33 | PMD to MDI optical specifications for 50/10GBASE-PQX-U3 .....                                                                                                                                 | 103 |

| 141.10.4.34 | PMD to MDI optical specifications for 50/25GBASE-PQG-U2 .....                                                                                                                                 | 103 |

| 141.10.4.35 | PMD to MDI optical specifications for 50/25GBASE-PQG-U3 .....                                                                                                                                 | 103 |

| 141.10.4.36 | PMD to MDI optical specifications for 50/25GBASE-PQX-U2 .....                                                                                                                                 | 103 |

| 141.10.4.37 | PMD to MDI optical specifications for 50/25GBASE-PQX-U3 .....                                                                                                                                 | 104 |

| 141.10.4.38 | PMD to MDI optical specifications for 50GBASE-PQG-U2 .....                                                                                                                                    | 104 |

| 141.10.4.39 | PMD to MDI optical specifications for 50GBASE-PQG-U3 .....                                                                                                                                    | 104 |

| 141.10.4.40 | PMD to MDI optical specifications for 50GBASE-PQX-U2 .....                                                                                                                                    | 104 |

| 141.10.4.41 | PMD to MDI optical specifications for 50GBASE-PQX-U3 .....                                                                                                                                    | 105 |

| 141.10.4.42 | Definitions of optical parameters and measurement methods .....                                                                                                                               | 105 |

| 141.10.4.43 | Characteristics of the fiber optic cabling and MDI .....                                                                                                                                      | 106 |

| 141.10.4.44 | Environmental specifications .....                                                                                                                                                            | 106 |

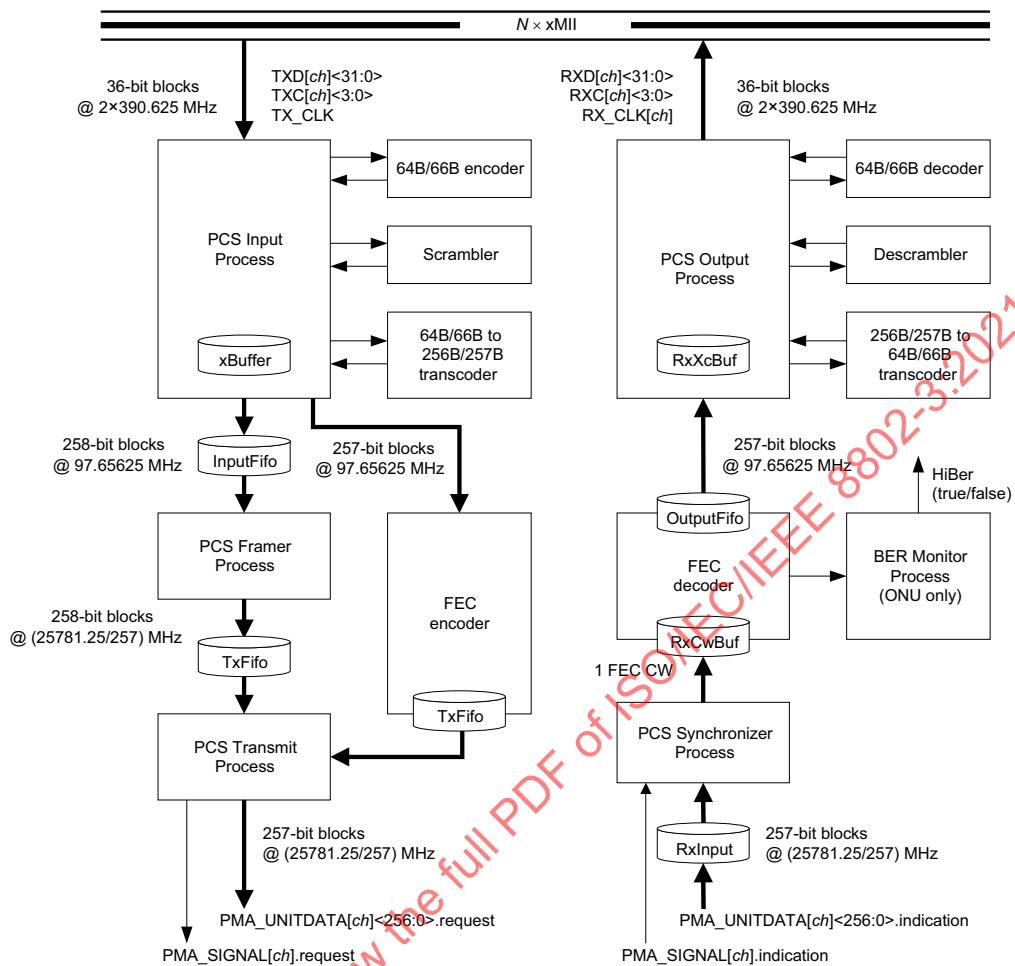

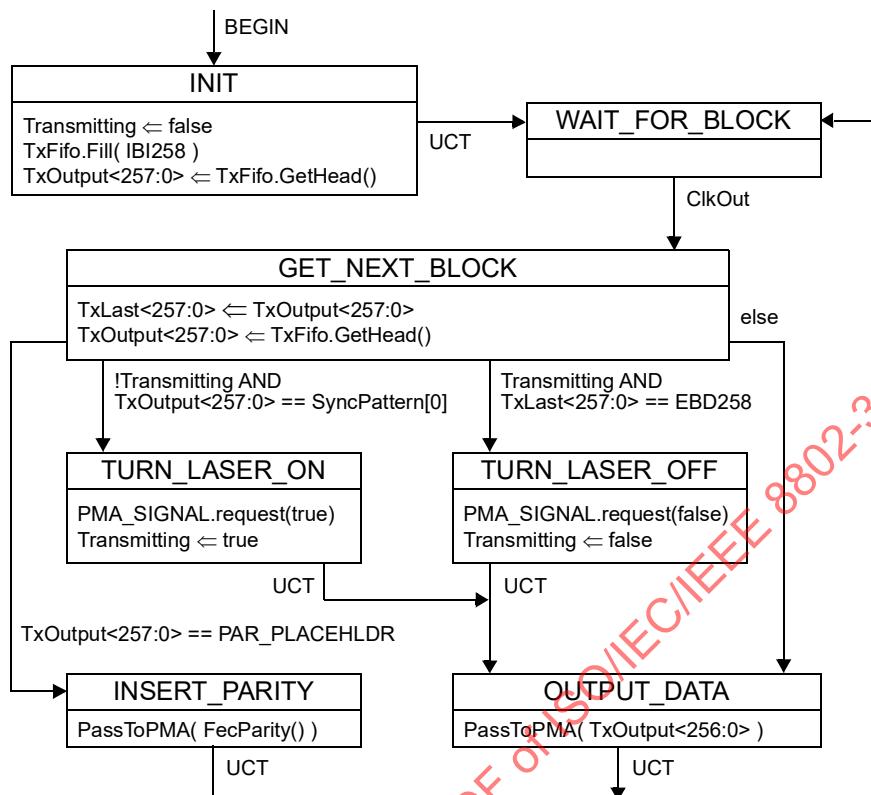

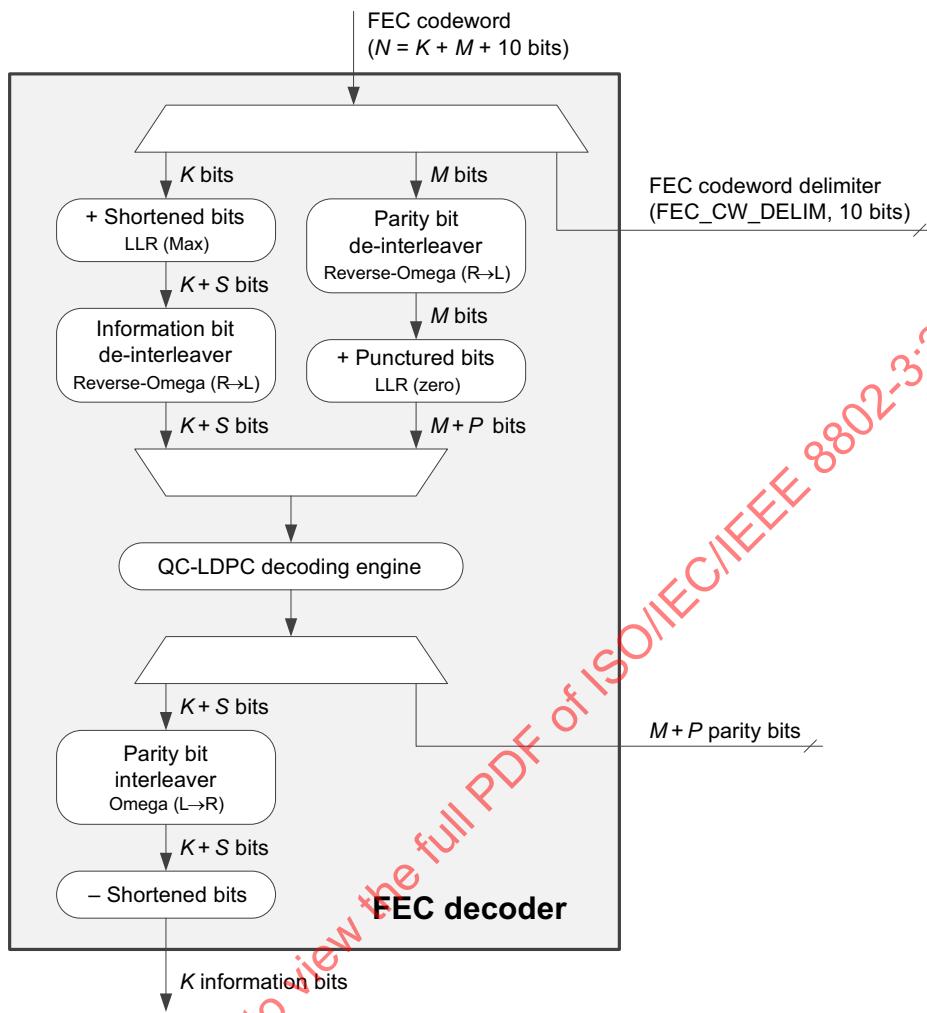

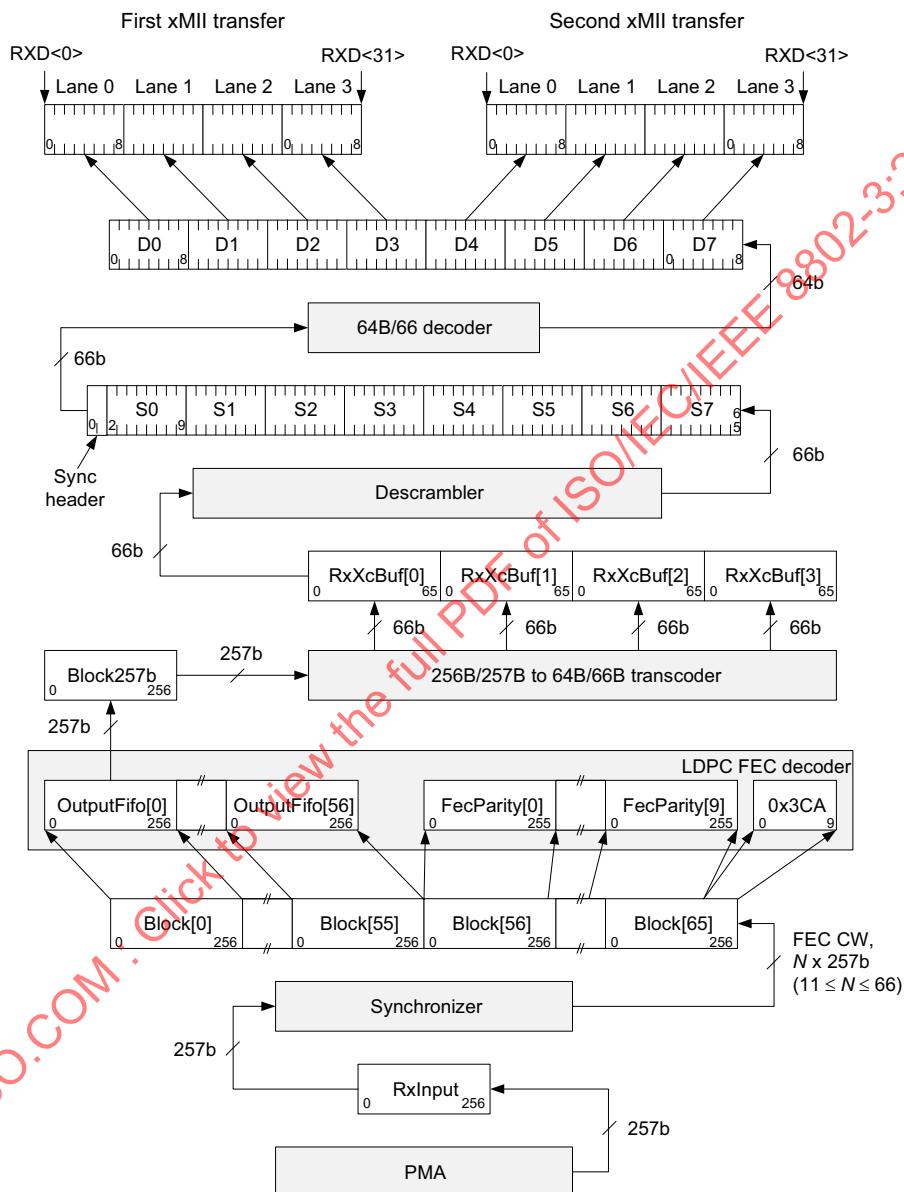

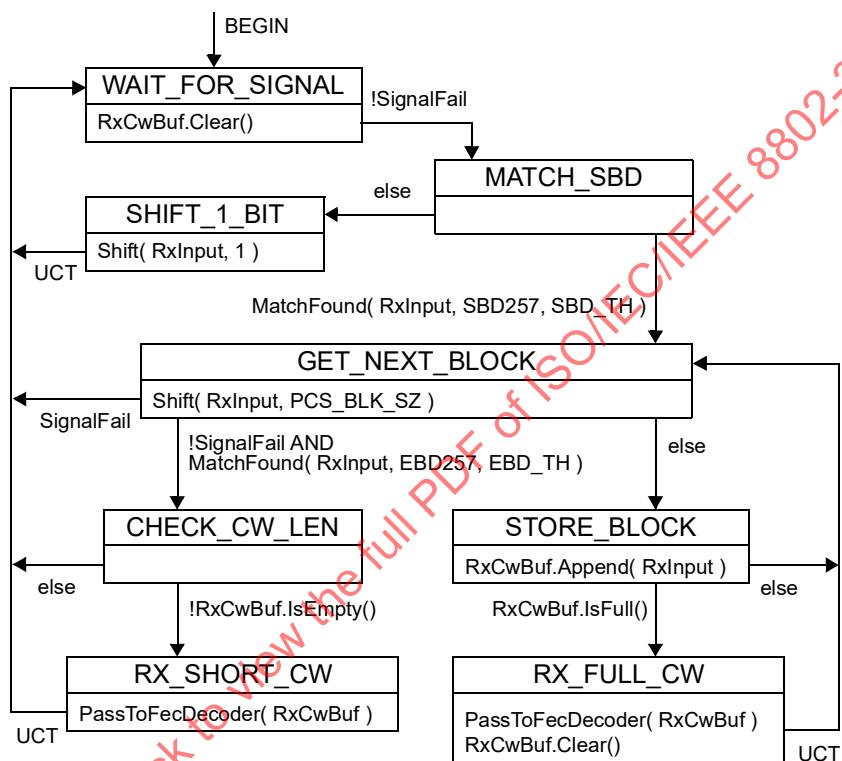

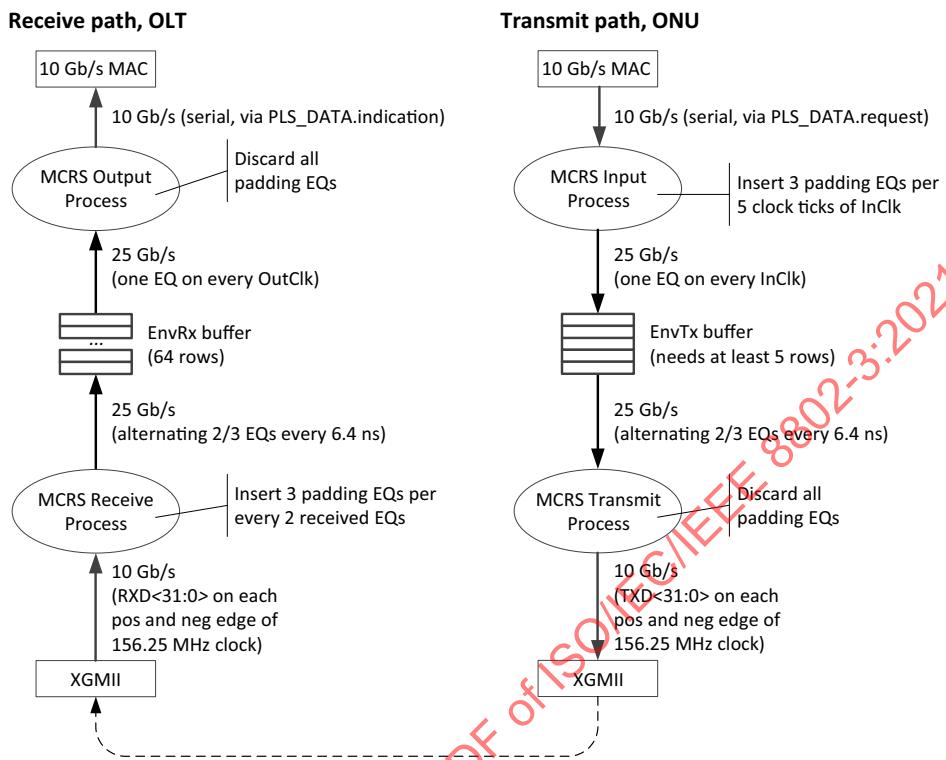

| 142.        | Physical Coding Sublayer and Physical Media Attachment for Nx25G-EPON .....                                                                                                                   | 107 |

| 142.1       | Overview .....                                                                                                                                                                                | 107 |

| 142.1.1     | Conventions .....                                                                                                                                                                             | 107 |

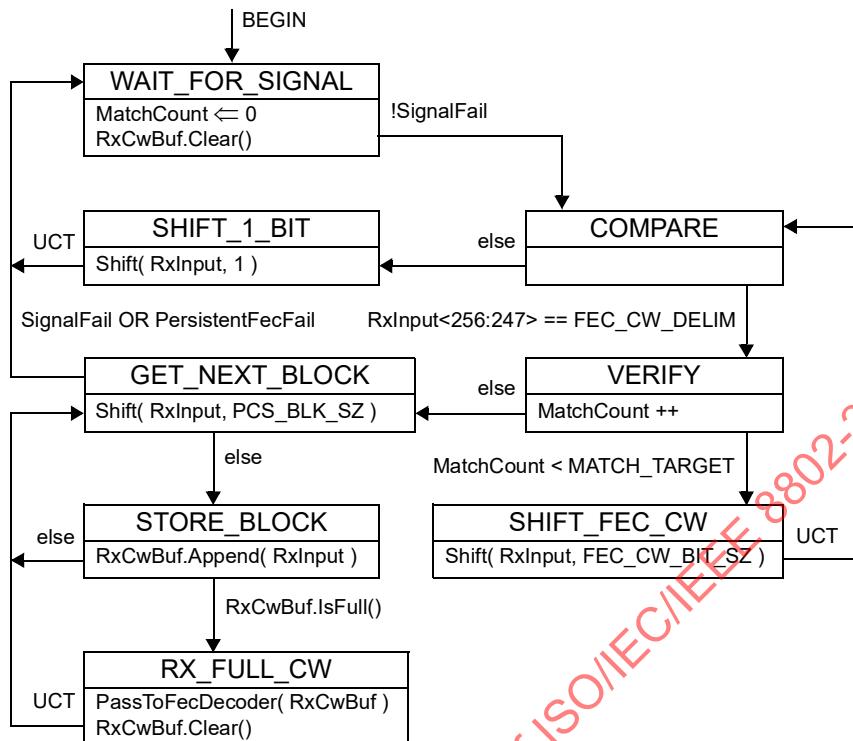

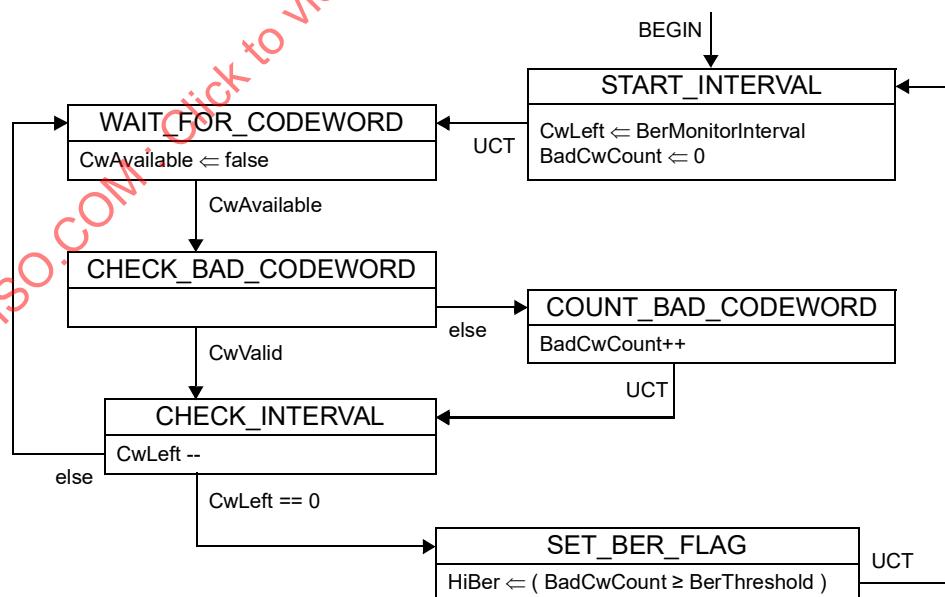

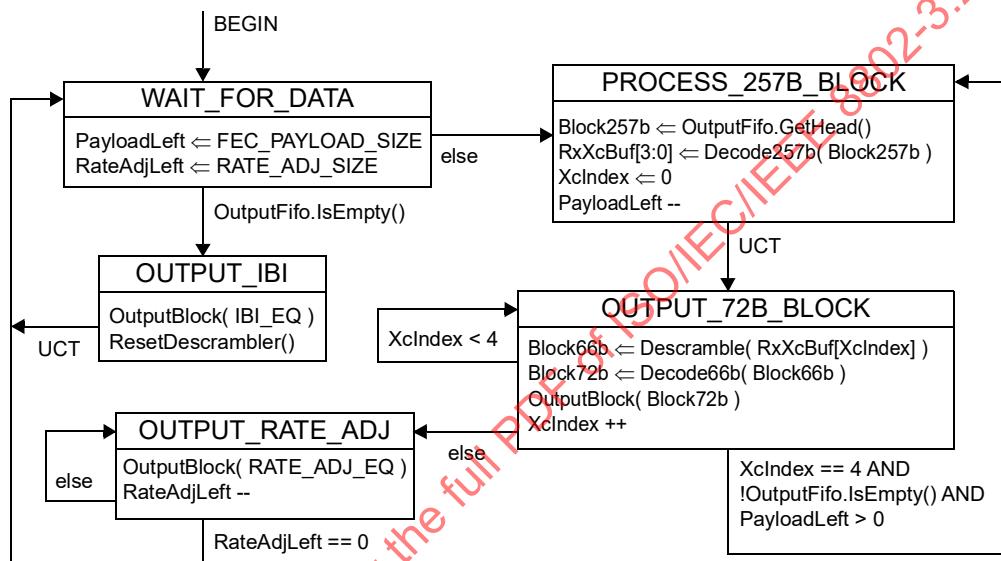

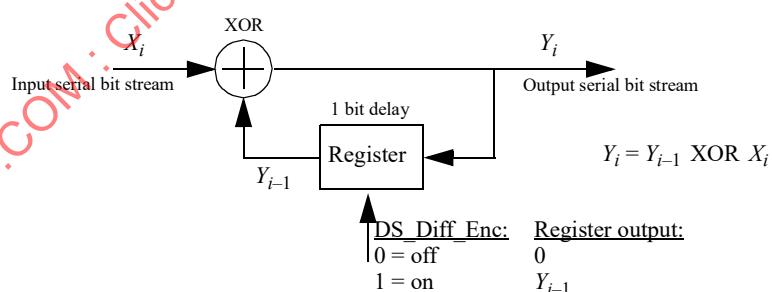

| 142.1.1.1   | State diagrams .....                                                                                                                                                                          | 107 |

| 142.1.1.2   | Hexadecimal notation .....                                                                                                                                                                    | 107 |

|             |                                                  |     |

|-------------|--------------------------------------------------|-----|

| 142.1.1.3   | Timers .....                                     | 110 |

| 142.1.1.4   | Operations on variables .....                    | 110 |

| 142.1.1.5   | Operations on wrap-around variables .....        | 111 |