# INTERNATIONAL STANDARD

IEC

61883-1

Second edition

2003-01

## Consumer audio/video equipment – Digital interface –

### Part 1: General

*Matériel audio/vidéo grand public –

Interface numérique –*

*Partie 1:

Généralités*

IECNORM.COM : Click to view the full PDF of IEC 61883-1:2003

Reference number

IEC 61883-1:2003(E)

## Publication numbering

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

## Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

## Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC, thus ensuring that the content reflects current technology. Information relating to this publication, including its validity, is available in the IEC Catalogue of publications (see below) in addition to new editions, amendments, and corrigenda. Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is also available from the following:

- **IEC Web Site ([www.iec.ch](http://www.iec.ch))**

- **Catalogue of IEC publications**

The on-line catalogue on the IEC web site ([http://www.iec.ch/searchpub/cur\\_fut.htm](http://www.iec.ch/searchpub/cur_fut.htm)) enables you to search by a variety of criteria including text searches, technical committees and date of publication. On-line information is also available on recently issued publications, withdrawn and replaced publications, as well as corrigenda.

- **IEC Just Published**

This summary of recently issued publications ([http://www.iec.ch/online\\_news/justpub/jp\\_entry.htm](http://www.iec.ch/online_news/justpub/jp_entry.htm)) is also available by email. Please contact the Customer Service Centre (see below) for further information.

- **Customer Service Centre**

If you have any questions regarding this publication or need further assistance, please contact the Customer Service Centre:

Email: [custserv@iec.ch](mailto:custserv@iec.ch)

Tel: +41 22 919 02 11

Fax: +41 22 919 03 00

# INTERNATIONAL STANDARD

IEC

61883-1

Second edition

2003-01

## Consumer audio/video equipment – Digital interface –

### Part 1: General

*Matériel audio/vidéo grand public –

Interface numérique –*

*Partie 1:

Généralités*

IECNORM.COM : Click to view the full PDF of IEC 61883-1:2003

© IEC 2003 — Copyright - all rights reserved

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: [inmail@iec.ch](mailto:inmail@iec.ch) Web: [www.iec.ch](http://www.iec.ch)

Commission Electrotechnique Internationale

International Electrotechnical Commission

Международная Электротехническая Комиссия

PRICE CODE

X

*For price, see current catalogue*

## CONTENTS

|                                                             |    |

|-------------------------------------------------------------|----|

| FOREWORD .....                                              | 4  |

| 1 Scope .....                                               | 6  |

| 2 Normative references .....                                | 6  |

| 3 Abbreviations .....                                       | 6  |

| 4 High performance serial bus layers .....                  | 7  |

| 4.1 Cable physical layer .....                              | 7  |

| 4.2 Link layer .....                                        | 7  |

| 4.3 Transaction layer .....                                 | 7  |

| 5 Minimum node capabilities .....                           | 7  |

| 5.1 Serial bus management .....                             | 7  |

| 5.2 Command and status registers .....                      | 7  |

| 6 Real time data transmission protocol .....                | 9  |

| 6.1 Common isochronous packet (CIP) format .....            | 9  |

| 6.2 Transmission of fixed length source packet .....        | 10 |

| 7 Isochronous data flow management .....                    | 11 |

| 7.1 General .....                                           | 11 |

| 7.2 Plugs and plug control registers .....                  | 11 |

| 7.3 Connections .....                                       | 12 |

| 7.4 Plug states .....                                       | 13 |

| 7.5 OUTPUT_MASTER_PLUG register definition .....            | 13 |

| 7.6 INPUT_MASTER_PLUG register definition .....             | 14 |

| 7.7 OUTPUT_PLUG_CONTROL register definition .....           | 14 |

| 7.8 INPUT_PLUG_CONTROL register definition .....            | 15 |

| 7.9 Plug control register modification rules .....          | 15 |

| 7.10 Bus reset .....                                        | 16 |

| 7.11 Plug control register access rules .....               | 16 |

| 8 Connection management procedures (CMP) .....              | 17 |

| 8.1 Introduction .....                                      | 17 |

| 8.2 Managing point-to-point connections .....               | 17 |

| 8.3 Managing broadcast-out connections .....                | 18 |

| 8.4 Managing broadcast-in connections .....                 | 18 |

| 8.5 Managing connections after a bus reset .....            | 19 |

| 9 Function control protocol (FCP) .....                     | 19 |

| 9.1 Introduction .....                                      | 19 |

| 9.2 Asynchronous packet structure .....                     | 20 |

| 9.3 FCP frame structure .....                               | 20 |

| Annex A (informative) Cables and connectors .....           | 41 |

| Figure 1 – Configuration ROM .....                          | 25 |

| Figure 2 – Isochronous packet .....                         | 26 |

| Figure 3 – CIP header .....                                 | 26 |

| Figure 4 – Model of transmission of source packets .....    | 26 |

| Figure 5 – Two quadlets CIP header (Form_0, Form_1=0) ..... | 27 |

| Figure 6 – Source packet header format .....                | 27 |

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| Figure 7 – Plug and PR usage .....                                              | 28 |

| Figure 8 – Connections.....                                                     | 28 |

| Figure 9 – Plug state diagram .....                                             | 29 |

| Figure 10 – oMPR format.....                                                    | 29 |

| Figure 11 – iMPR format.....                                                    | 30 |

| Figure 12 – oPCR format.....                                                    | 30 |

| Figure 13 – iPCR format.....                                                    | 31 |

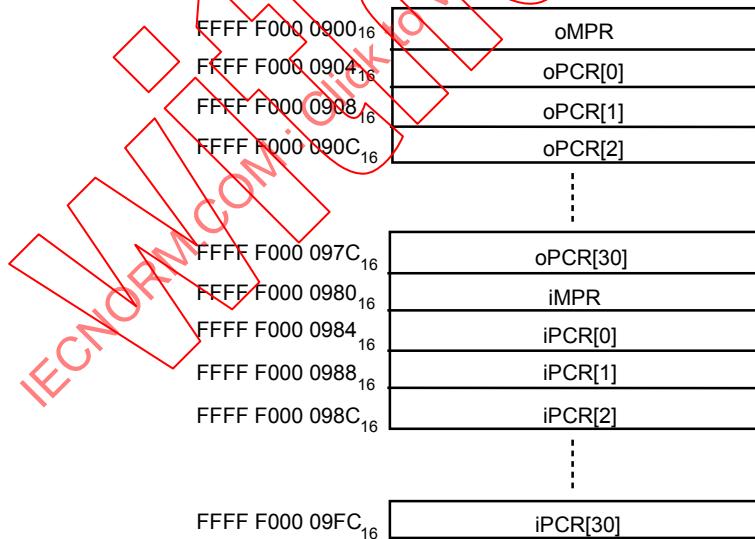

| Figure 14 – PCR address map.....                                                | 31 |

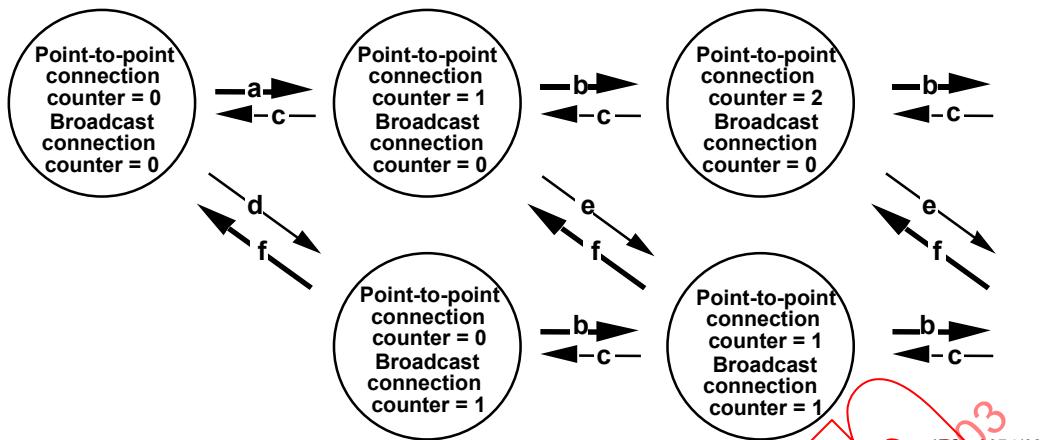

| Figure 15 – Point-to-point and broadcast connection counter modifications ..... | 32 |

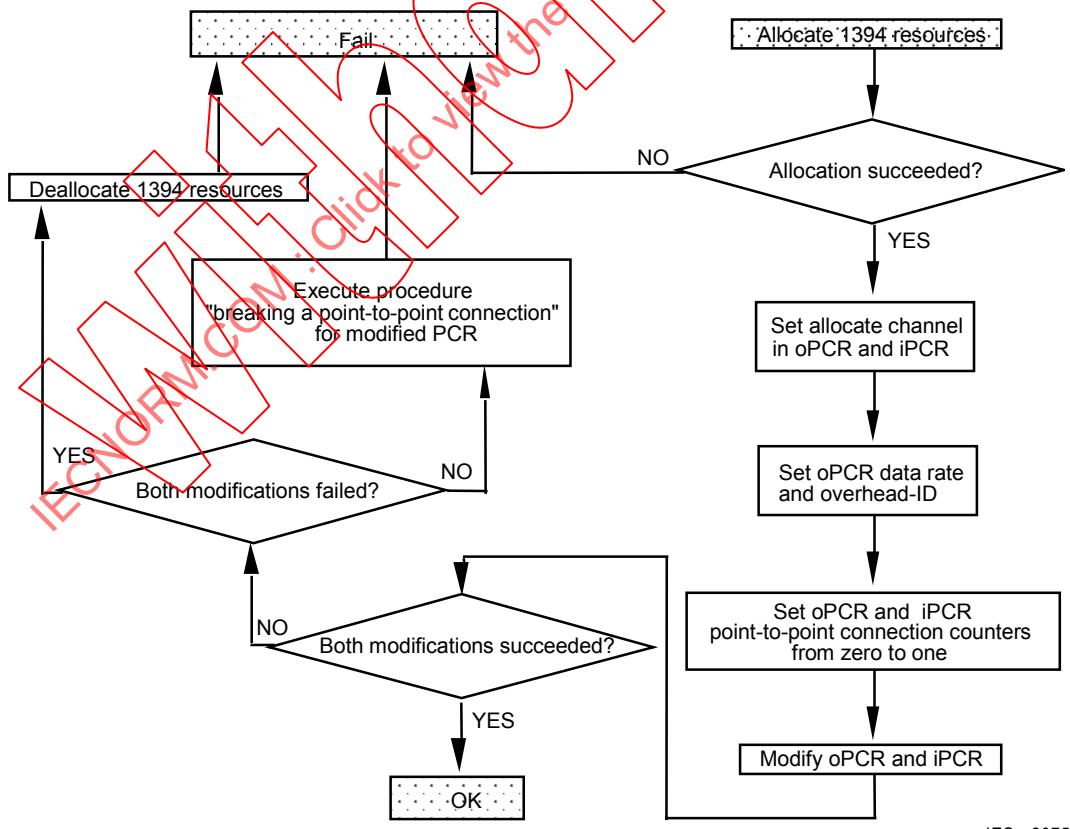

| Figure 16 – Establishing a point-to-point connection.....                       | 32 |

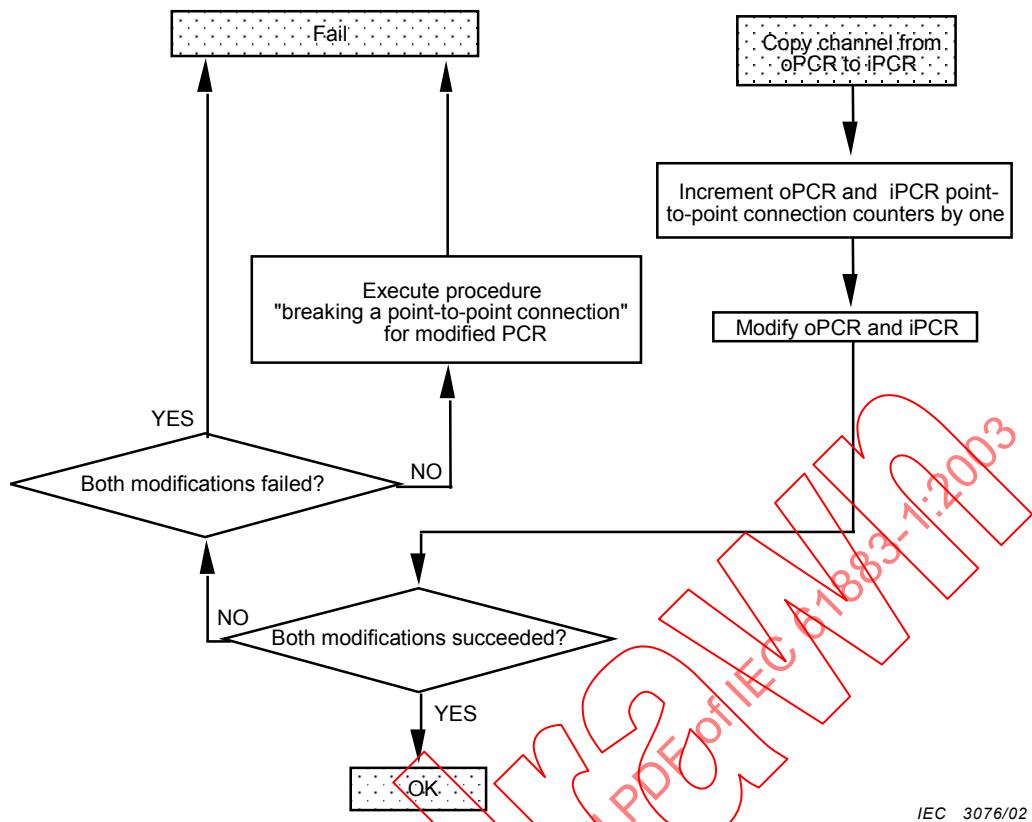

| Figure 17 – Overlaying a point-to-point connection.....                         | 33 |

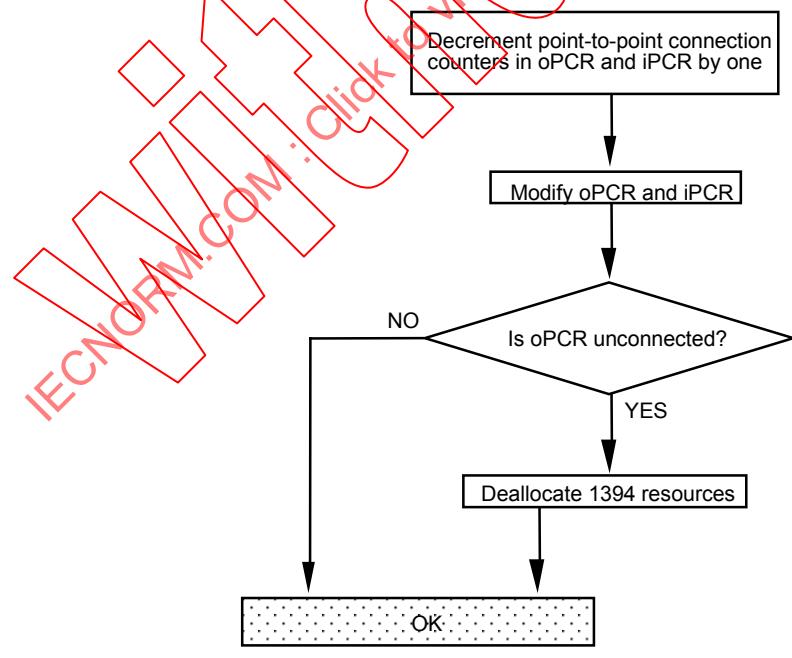

| Figure 18 – Breaking a point-to-point connection.....                           | 33 |

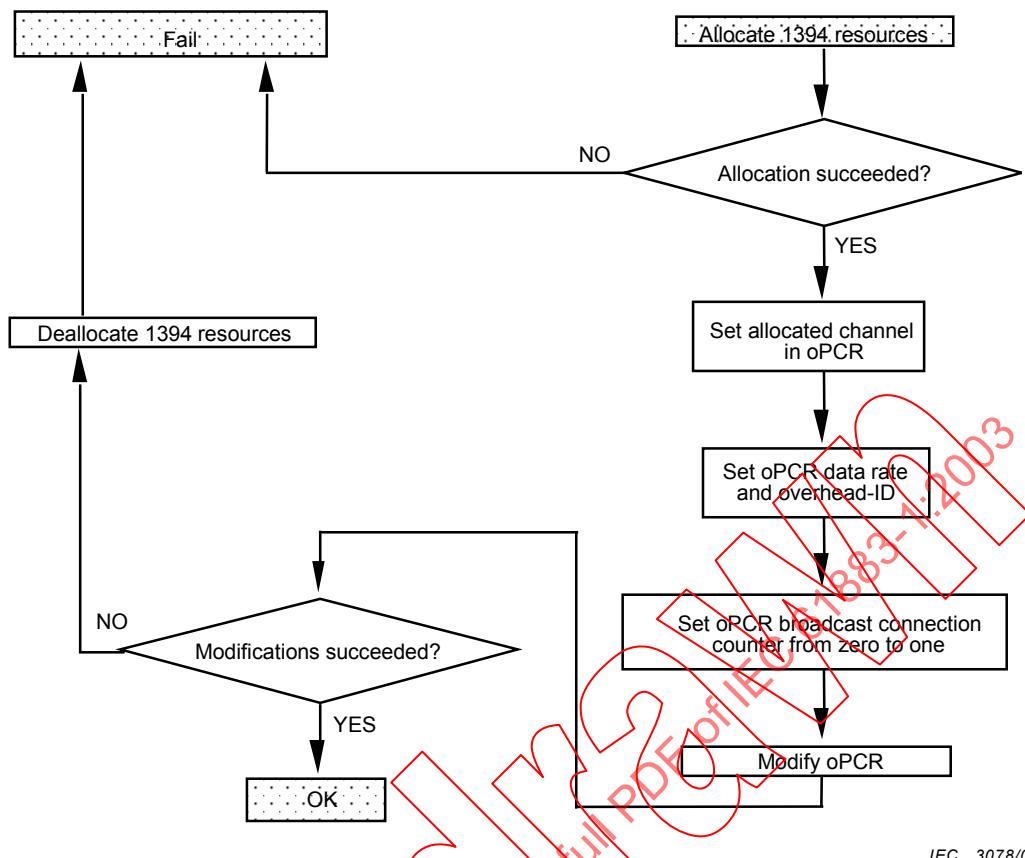

| Figure 19 – Establishing a broadcast-out connection.....                        | 34 |

| Figure 20 – Overlaying a broadcast-out connection .....                         | 34 |

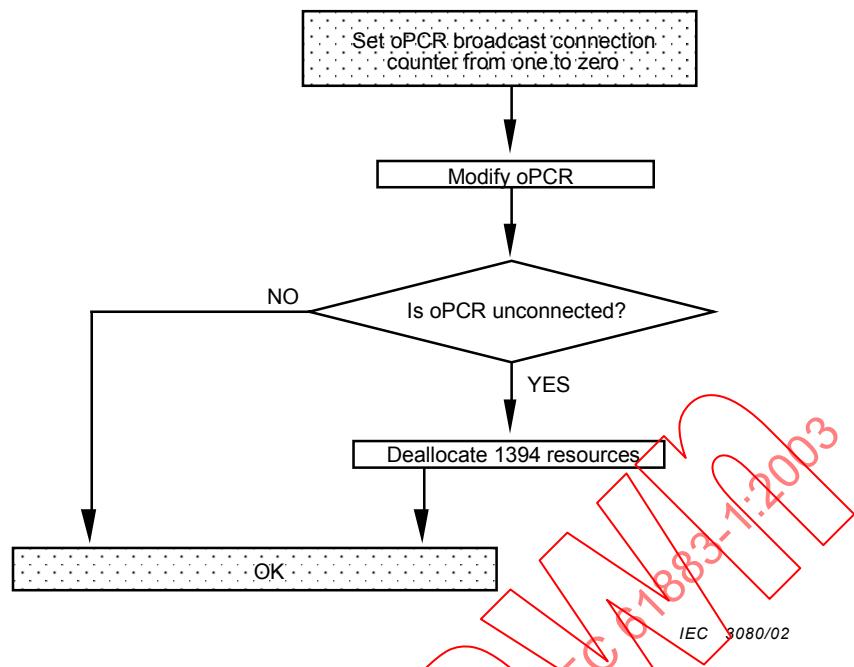

| Figure 21 – Breaking a broadcast-out connection.....                            | 35 |

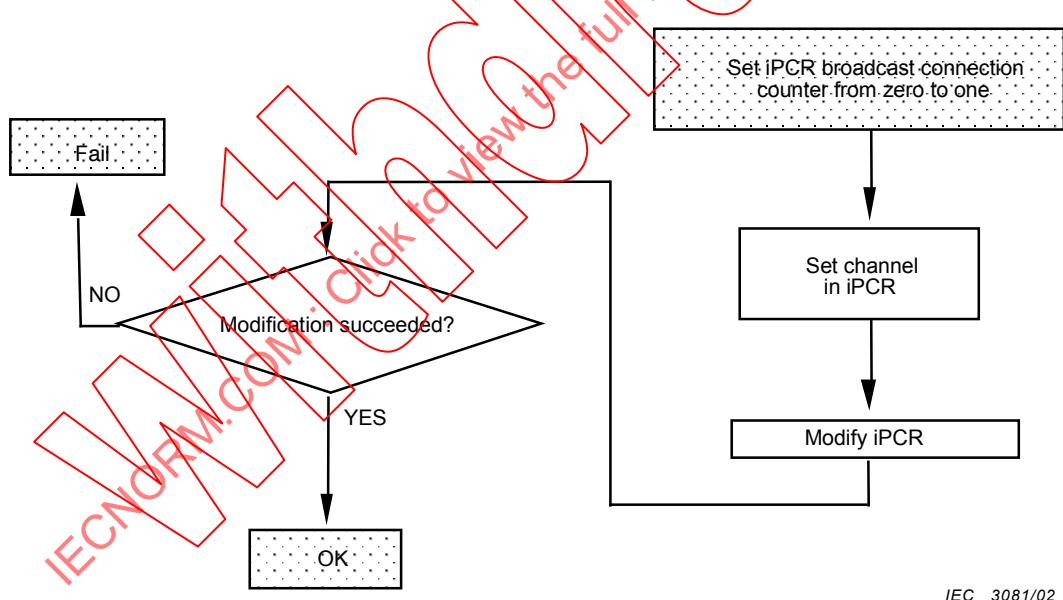

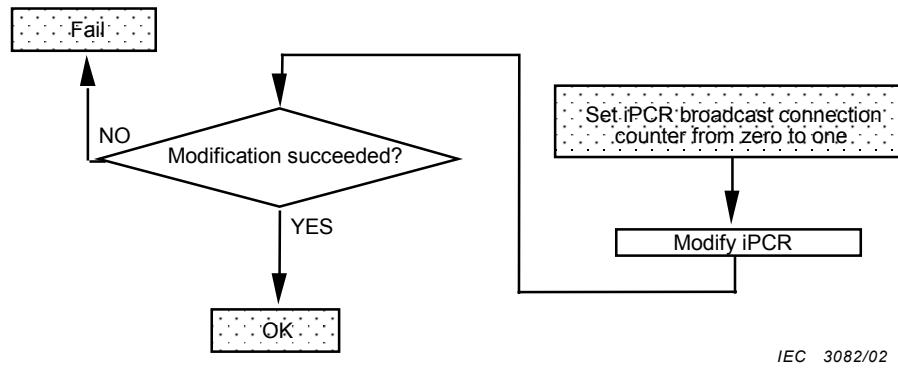

| Figure 22 – Establishing a broadcast-in connection.....                         | 35 |

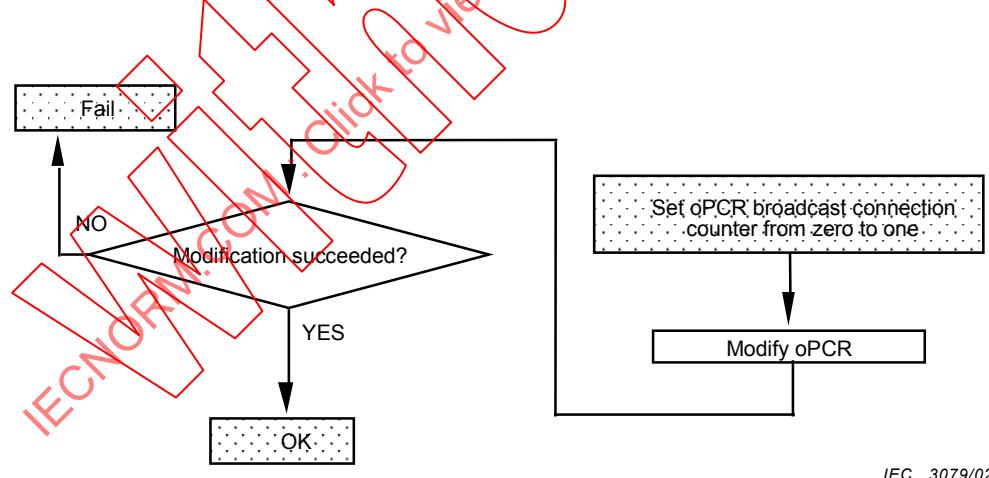

| Figure 23 – Overlaying a broadcast-in connection .....                          | 36 |

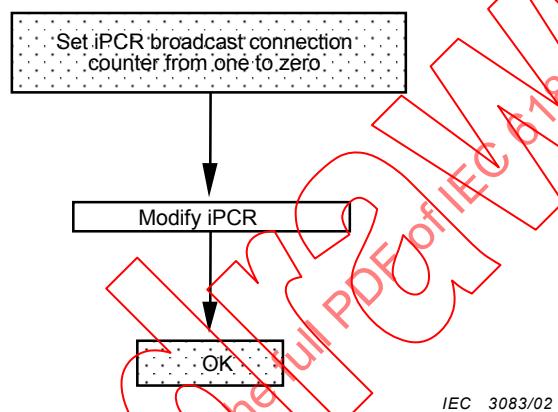

| Figure 24 – Breaking a broadcast-in connection.....                             | 36 |

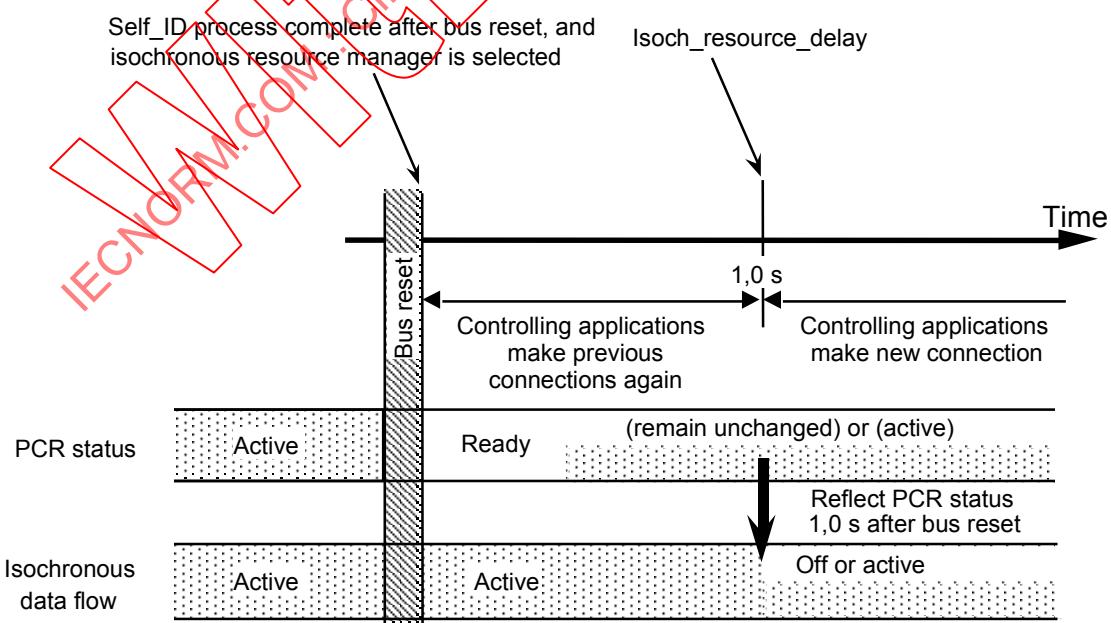

| Figure 25 – Time chart of connection management and PCR activities .....        | 36 |

| Figure 26 – Restoring a point-to-point connection .....                         | 37 |

| Figure 27 – Restoring a broadcast-out connection.....                           | 37 |

| Figure 28 – Restoring a broadcast-in connection .....                           | 38 |

| Figure 29 – Command register and response register .....                        | 38 |

| Figure 30 – Write request for data block packet of IEEE 1394 .....              | 39 |

| Figure 31 – Write request for data quadlet packet of IEEE 1394.....             | 39 |

| Figure 32 – FCP frame structure.....                                            | 40 |

| Figure 33 – Vendor unique frame format .....                                    | 40 |

| Figure A.1 – Connector plug (6-pin) .....                                       | 41 |

| Figure A.2 – Connector socket (6-pin).....                                      | 42 |

| Figure A.3 – Connector plug (4-pin) .....                                       | 43 |

| Figure A.4 – Connector socket (4-pin).....                                      | 43 |

| Figure A.5 – Cable assembly schematic (6-pin).....                              | 44 |

| Figure A.6 – Cable assembly schematic (4-pin).....                              | 44 |

| Figure A.7 – Cable assembly schematic (4-pin to 6-pin) .....                    | 45 |

| Table 1 – Code allocation of FN.....                                            | 21 |

| Table 2 – Placing of data block sequence .....                                  | 21 |

| Table 3 – Code allocation of FMT .....                                          | 21 |

| Table 4 – Time stamp field of source packet header .....                        | 22 |

| Table 5 – Time stamp of SYT field .....                                         | 22 |

| Table 6 – oMPR and iMPR data rate capability and oPCR data rate encoding.....   | 22 |

| Table 7 – oPCR overhead ID encoding .....                                       | 23 |

| Table 8 – CTS: Command/transaction set encoding .....                           | 23 |

| Table 9 – Unit_SW_Version code assignment.....                                  | 24 |

## INTERNATIONAL ELECTROTECHNICAL COMMISSION

**CONSUMER AUDIO/VIDEO EQUIPMENT –

DIGITAL INTERFACE –****Part 1: General****FOREWORD**

- 1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, the IEC publishes International Standards. Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested National Committees.

- 3) The documents produced have the form of recommendations for international use and are published in the form of standards, technical specifications, technical reports or guides and they are accepted by the National Committees in that sense.

- 4) In order to promote international unification, IEC National Committees undertake to apply IEC International Standards transparently to the maximum extent possible in their national and regional standards. Any divergence between the IEC Standard and the corresponding national or regional standard shall be clearly indicated in the latter.

- 5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with one of its standards.

- 6) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 61883-1 has been prepared by technical area 4, Digital system interfaces, of IEC technical committee 100: Audio, video and multimedia systems and equipment.

This second edition of IEC 61883-1 cancels and replaces the first edition, published in 1998, of which it constitutes a technical revision.

The text of this standard is based on the following documents:

| FDIS         | Report on voting |

|--------------|------------------|

| 100/557/FDIS | 100/609/RVD      |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

International Standard IEC 61883 consists of the following parts under the general title *Consumer audio/video equipment – Digital interface*:

Part 1: General

Part 2: SD-DVCR data transmission

Part 3: HD-DVCR data transmission

Part 4: MPEG2-TS data transmission

Part 5: SDL-DVCR data transmission

Part 6: Audio and music data transmission protocol

Part 7: Transmission of ITU-R BO.1294 System B

The committee has decided that the contents of this publication will remain unchanged until 2005.

At this date, the publication will be

- reconfirmed;

- withdrawn;

- replaced by a revised edition, or

- amended.

IECNORM.COM : Click to view the full PDF of IEC 61883-1:2003

## CONSUMER AUDIO/VIDEO EQUIPMENT – DIGITAL INTERFACE –

### Part 1: General

#### 1 Scope

This part of IEC 61883 specifies a digital interface for consumer electronic audio/video equipment using IEEE 1394, High Performance Serial Bus. It describes the general packet format, data flow management and connection management for audio-visual data, and also the general transmission rules for control commands.

The object of this standard is to define a transmission protocol for audio-visual data and control commands which provides for the interconnection of digital audio and video equipment, using IEEE 1394.

#### 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEEE 1212:2001, *Standard for a Control and Status Registers (CSR) Architecture for microcomputer buses*

IEEE 1394:1995, *Standard for a High Performance Serial Bus*

IEEE 1394a:2000, *Standard for a High Performance Serial Bus – Amendment 1*

NOTE Throughout this document, the term "IEEE 1394" indicates a reference to the standard that is the result of the editorial combination of IEEE 1394:1995 and IEEE 1394a:2000. Devices conforming solely to IEEE 1394:1995 may conform to IEC 61883. Devices conforming to IEC 61883 should conform to IEEE 1394a:2000.

#### 3 Abbreviations

For the purpose of this part of IEC 61883, the following abbreviations apply:

|      |                                  |

|------|----------------------------------|

| AV/C | Audio Video Control              |

| CHF  | CIP Header Field                 |

| CIP  | Common Isochronous Packet        |

| CMP  | Connection Management Procedures |

| CSR  | Command and Status Register      |

| CTS  | Command/Transaction Set          |

| CRC  | Cyclic Redundancy Check Code     |

| DVCR | Digital Video Cassette Recorder  |

| EOH  | End of CIP Header                |

| FCP  | Function Control Protocol        |

| iPCR | Input Plug Control Register      |

| iMPR | Input Master Plug Register       |

| MPEG | Motion Picture Experts Group     |

| oPCR | Output Plug Control Register     |

| oMPR | Output Master Plug Register      |

| ROM  | Read Only Memory                 |

## 4 High performance serial bus layers

### 4.1 Cable physical layer

All cable physical layer implementations conforming to this standard shall meet the performance criteria specified by IEEE 1394. Either the cable and connector defined in IEEE 1394:1995, or the cables and connector defined in IEEE 1394a:2000, shall be used.

When necessary for an AV device to generate a bus reset, it shall follow the requirements of IEEE 1394a:2000, 8.2.1. An AV device that initiates a bus reset should generate an arbitrated (short) bus reset, as specified by IEEE 1394a:2000, in preference to the long bus reset defined by IEEE 1394:1995.

### 4.2 Link layer

All link layer implementations conforming to this standard shall meet the specifications of IEEE 1394.

### 4.3 Transaction layer

All transaction layer implementations conforming to this standard shall meet the specifications of IEEE 1394.

## 5 Minimum node capabilities

A node shall conform to the following requirements:

- a node shall be cycle master capable. This is because every node has the possibility to be assigned as a root;

- a node shall be isochronous resource manager capable, as specified by IEEE 1394:1995, and shall implement the additional isochronous resource manager facilities and responsibilities specified by IEEE 1394a:2000 in subclauses 8.3.1.5, 8.3.2.3.8, 8.3.2.3.11, 8.4.2.3 and 8.4.2.6A;

- a node which transmits or receives isochronous packets shall have plug control registers (see 7.2).

### 5.1 Serial bus management

Bus manager capability is optional for AV devices, but, if implemented by devices conforming to this standard, shall conform to IEEE 1394.

### 5.2 Command and status registers

#### 5.2.1 CSR core registers

This standard conforms to the CSR architecture. Details of its registers are specified by IEEE 1394.

The STATE\_CLEAR.cmstr bit shall be implemented as specified by IEEE 1394a:2000, 8.3.2.2.1.

**NOTE** The cmstr bit is set automatically (see IEEE 1394a:2000, 8.3.2.2.1) by system software or hardware when a node becomes the new root after the bus reset process is completed. In this manner, it is possible to ensure the fast resumption and continuity of data transmission where the time scale is critical at the level of microseconds. The rapid activation of a new cycle master decreases the likelihood of a gap in the transmission of cycle start packets; uninterrupted transmission of cycle start packets at nominal 125 µs intervals is critical to the delivery of isochronous data within its latency requirements.

## 5.2.2 Serial bus node registers

Implementation requirements for bus-dependent registers in this standard conform to IEEE 1394. A node shall have the following registers:

- CYCLE\_TIME register

- BUS\_TIME register

- BUS\_MANAGER\_ID register

- BANDWIDTH\_AVAILABLE register

- CHANNELS\_AVAILABLE register

A node should have the following register specified by IEEE 1394a:2000:

- BROADCAST\_CHANNEL register

## 5.2.3 Configuration ROM requirements

A node shall implement the general ROM format as defined in IEEE 1212:2001 and IEEE 1394. Additional information required for implementations of this standard shall be included in one of the unit directories. Figure 1 shows an example of the configuration ROM implementation for this standard.

### 5.2.3.1 Bus\_Info\_Block entry

Implementation requirements for the Bus\_Info\_Block in this standard shall conform to IEEE 1394.

### 5.2.3.2 Root directory

The following entries shall be present:

- Module\_Vendor\_ID;

- Node\_Capabilities;

- Unit\_Directory (offset to a unit directory defined by this standard).

Other entries may be implemented in addition to the above required entries.

### 5.2.3.3 Unit directory

The following entries shall be present:

- Unit\_Spec\_ID;

- Unit\_SW\_Version.

The value of the Unit\_Spec\_ID and the Unit\_SW\_Version for this standard are given as follows:

|                  |              |                    |

|------------------|--------------|--------------------|

| Unit_Spec_ID:    | First octet  | = 00 <sub>16</sub> |

|                  | Second octet | = A0 <sub>16</sub> |

|                  | Third octet  | = 2D <sub>16</sub> |

| Unit_SW_Version: | First octet  | = 01 <sub>16</sub> |

The second and third octets of Unit\_SW\_Version for this standard are specified in Table 9 and indicate capabilities for command/transaction sets. The Unit\_SW\_Version field is used to identify which protocol is supported by the device. If a device supports more than one protocol, the device shall have a separate unit directory for each protocol supported.

## 6 Real time data transmission protocol

### 6.1 Common isochronous packet (CIP) format

#### 6.1.1 Isochronous packet structure

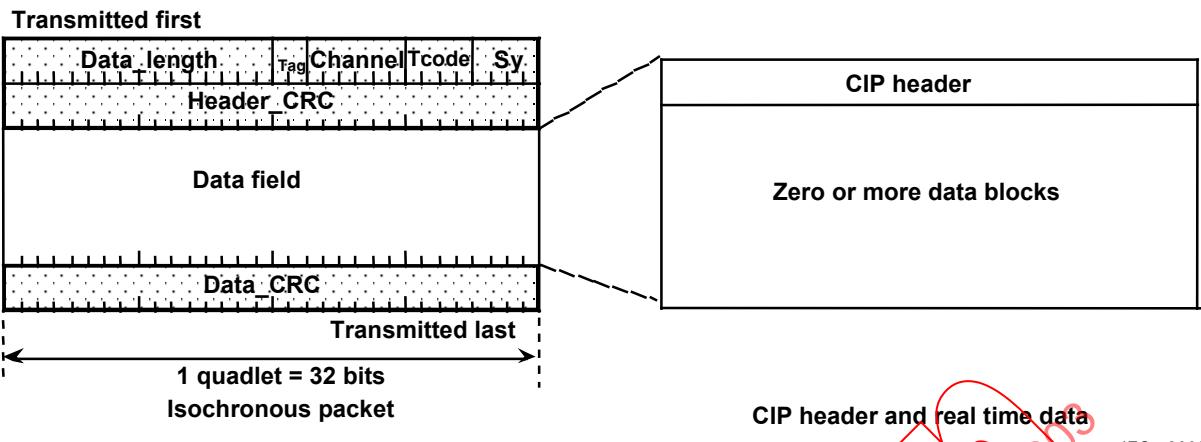

The structure of the isochronous packet utilized by this standard is illustrated in Figure 2. The packet header and header CRC are the first two quadlets of an IEEE 1394 isochronous packet. The CIP header is placed at the beginning of the data field of an IEEE 1394 isochronous packet, immediately followed by zero or more data blocks.

#### 6.1.2 Packet header structure

The packet header consists of the following items as specified in IEEE 1394.

Data\_length: specifies the length of the data field of the isochronous packet in bytes, which is determined as follows:

$$\text{CIP header size} + \text{signal data size}$$

Tag: provides a high level label for the format of data carried by the isochronous packet.

$00_2$  = No CIP header included

$01_2$  = CIP header included as specified in 6.1.3

$10_2$  = Reserved

$11_2$  = Reserved

Channel: specifies the isochronous channel number for the packet.

Tcode: specifies the packet format and the type of transaction that shall be performed (fixed at  $1010_2$ ).

Sy: application-specific control field.

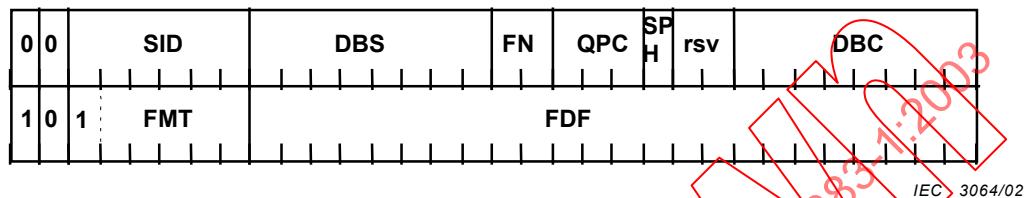

#### 6.1.3 CIP header structure

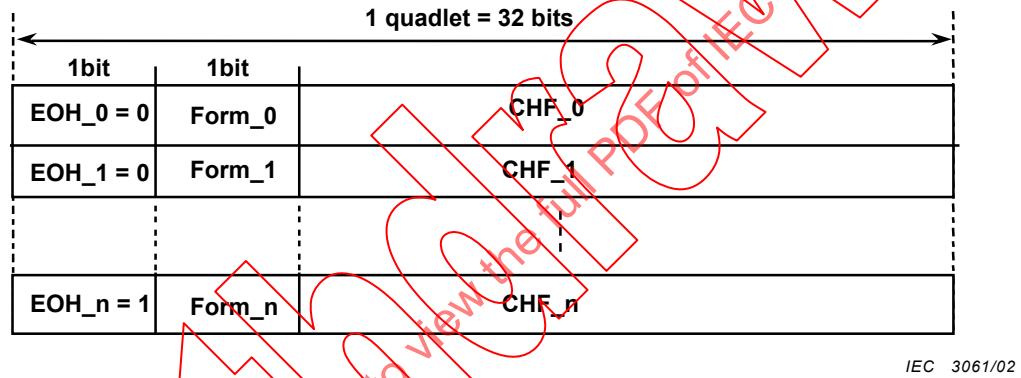

The CIP header is placed at the beginning of the data field of an IEEE 1394 isochronous packet. It contains information on the type of the real time data contained in the data field following it. The structure of the CIP header is shown in Figure 3.

The definitions of the fields are given as follows:

EOH\_n (End of CIP header): means the last quadlet of a CIP header.

0 = Another quadlet will follow

1 = The last quadlet of a CIP header

Form\_n: in combination with EOH, shows the additional structure of CHF\_n.

CHF\_n (CIP header field): CIP header field of n<sup>th</sup> quadlet. The additional structure of CHF\_n depends on EOH\_0, form\_0, EOH\_1, form\_1, ... EOH\_n, and form\_n.

## 6.2 Transmission of fixed length source packet

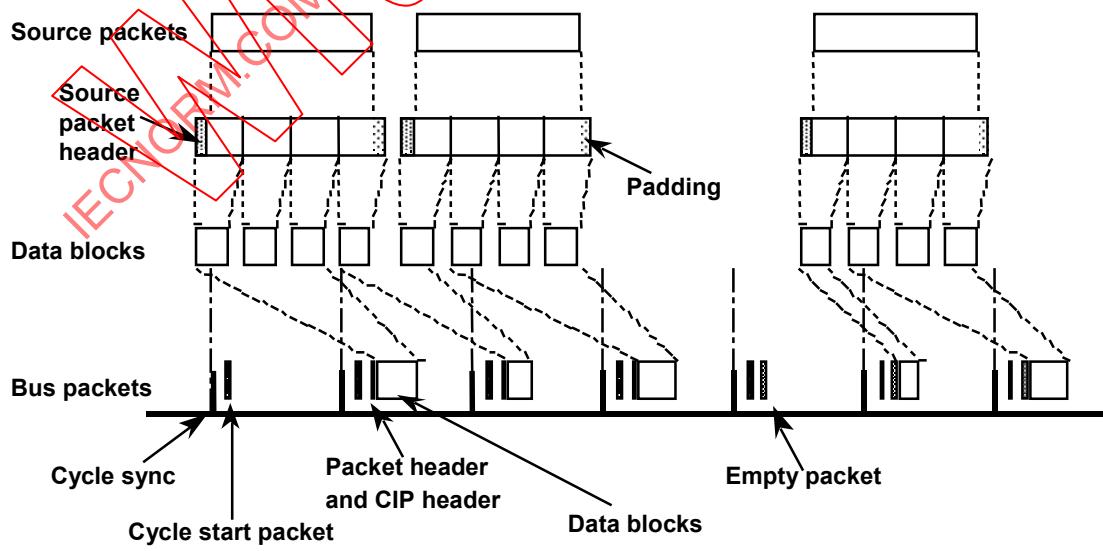

This protocol transfers a stream of source packets from an application on a device to an application on other device(s). A source packet is assumed to have a fixed length, which is defined for each type of data. The data rate can be variable.

A source packet may be split into 1, 2, 4 or 8 data blocks, and zero or more data blocks are contained in an IEEE 1394 isochronous packet. A receiver of the packet shall collect the data blocks in the isochronous packet and combine them to reconstruct the source packet to send to the application.

A model conforming to these requirements is shown in Figure 4.

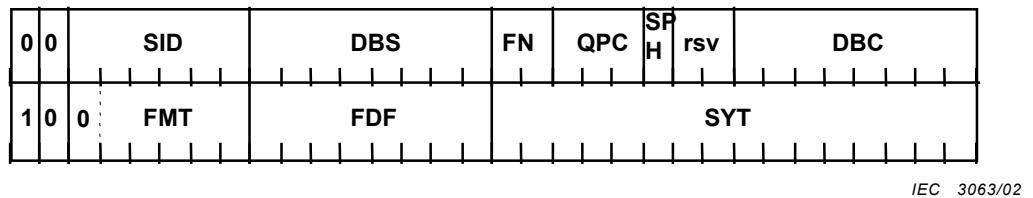

### 6.2.1 Two-quadlet CIP header (form\_0=0, form\_1=0)

This standard defines the two-quadlet CIP header for a fixed length source packet. There are two types for the structure of the two-quadlet CIP header as shown in Figure 5. One is the CIP header with SYT field (Figure 5a), and the other is the CIP header without SYT field (Figure 5b). If a device transmits real time data (identified by FMT) and requires time stamp in the CIP header, it shall use the SYT format.

The definitions of the fields are given as follows.

- SID: Source node ID (node ID of transmitter)

- DBS: Data block size in quadlets.

DBS field is 8 bits because 256 quadlets is the maximum payload size for S100 mode. When 8 bits are all 0, it means 256 quadlets; and  $00000001_2$  to  $11111111_2$  means 1 quadlet to 255 quadlets accordingly.

|                       |                |

|-----------------------|----------------|

| 00000000 <sub>2</sub> | = 256 quadlets |

| 00000001 <sub>2</sub> | = 1 quadlet    |

| 00000010 <sub>2</sub> | = 2 quadlets   |

| .....                 | .....          |

| 11111111 <sub>2</sub> | = 255 quadlets |

Several data blocks may be put into a bus packet, which is a packet to be transmitted on the bus, if a higher bandwidth is required for S200 and S400 speed.

NOTE S100, S200 and S400 are transmission speeds as defined in IEEE 1394.

- FN: Fraction number.

The number of data blocks into which a source packet is divided. The allowable numbers and allocated FN codes are listed in Table 1.

- QPC: Quadlet padding count (0 quadlet to 7 quadlets).

The number of dummy quadlets padded at the end of every source packet to enable division into equally sized data blocks. The value of all bits in padding quadlets is always zero.

The number of padding quadlets shall be less than the number of data blocks into which every source packet is divided, as encoded by FN.

The number of padding quadlets shall be less than the size of a single data block, as encoded by DBS. Consequently, a data block shall never consist entirely of padding quadlets.

- SPH: Source packet header.

The value one indicates that the source packet has a source packet header. The format of the source packet header is shown in Figure 6. Code allocation of the time stamp field is shown in Table 4. When a time stamp is indicated, the time stamp field shall be encoded as the lower 25 bits of the IEEE 1394 CYCLE\_TIME register. Other bits are reserved for future extension and shall be zeros.

- Rsv: Reserved for future extension and shall be zeros.

- DBC: Continuity counter of data blocks for detecting a loss of data blocks

The value refers to the first data block following the CIP header in the bus packet. The lower FN bits contain the sequence number of the data block within its source packet. The remaining 8-FN bits form the sequence number of the source packet. The first data block of any source packet always has a sequence number with value zero. If FN is zero, then all 8 bits of DBC are used to represent a source packet sequence number. See also Table 2.

- FMT: Format ID.

The code allocation is illustrated in Table 3.

If FMT is  $111111_2$  (no data), the fields for DBS, FN, QPC, SPH and DBC are ignored and no data blocks shall be transmitted. For other values of FMT, data is present and the most significant bit of the FMT field indicates whether or not a time stamp in SYT format is present. When the most significant bit of FMT is zero, the FMT-dependent field contains a time stamp in the format specified by SYT. Otherwise the contents of the FMT-dependent field are unspecified. See also Figure 5 and Table 3.

- FDF: Format dependent field.

This field is defined for each FMT.

- SYT: The code allocation of the SYT field is shown in Table 5. When a time stamp is indicated by the most significant bit of the FMT field, the SYT field shall be encoded as the lower 16 bits of the IEEE 1394 CYCLE\_TIME register.

### 6.2.2 Isochronous packet transmission

Active transmitters shall send an isochronous packet in every cycle. If no data block is available, an empty packet shall be sent. An empty packet shall always contain a two-quadlet CIP header. The DBC field of an empty packet shall show the count for the first data block contained in the first non-empty IEEE 1394 isochronous packet for the same transmission stream following this empty packet. The other fields shall match the fields of the CIP header of non-empty packets on the same transmission stream.

## 7 Isochronous data flow management

### 7.1 General

To start and stop isochronous data flows on the bus and to control their attributes, the concept of plugs and plug control registers is used. Plug control registers are special purpose CSR registers.

**NOTE** Plugs do not physically exist on an AV device. Only the concept of a plug is used to establish an analogy with existing AV devices where each flow of information is routed via a physical plug.

This clause describes the contents of the plug control registers and how they may be modified. The set of procedures that use the plug control registers to control an isochronous data flow are called connection management procedures (CMP). The CMP that shall be used by AV devices are described in Clause 8.

### 7.2 Plugs and plug control registers

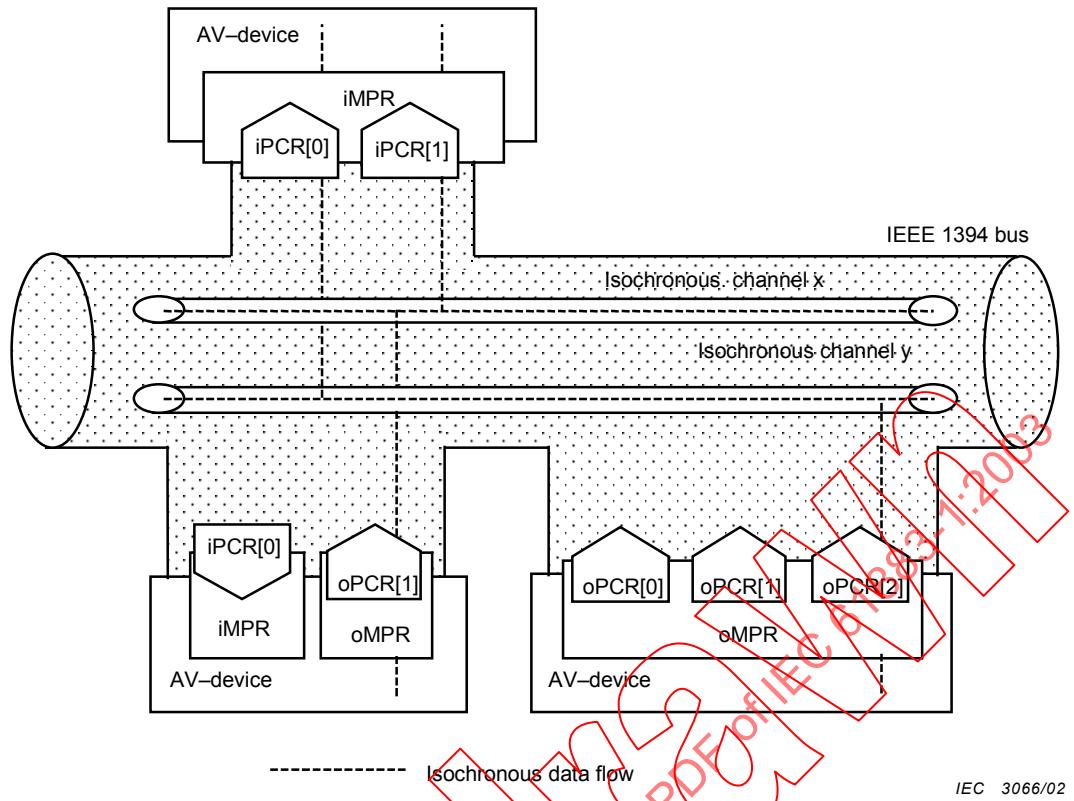

An isochronous data flow flows from one transmitting AV device to zero or more receiving AV devices by sending isochronous packets on one isochronous channel of the IEEE 1394 bus. An isochronous channel shall carry not more than one isochronous data flow and each isochronous data flow shall be carried on one isochronous channel.

Each isochronous data flow is transmitted to an isochronous channel through one output plug on the transmitting AV device and it is received from that isochronous channel through one input plug on each of the receiving AV devices. Each input and output plug shall not carry more than one isochronous data flow.

The transmission of an isochronous data flow through an output plug is controlled by one output plug control register (oPCR) and one output master plug register (oMPR) located on the transmitting AV device. On each AV device there is only one OUTPUT\_MASTER\_PLUG register for all output plugs. The OUTPUT\_MASTER\_PLUG register controls all attributes that are common to all isochronous data flows transmitted by the corresponding AV device. The OUTPUT\_PLUG\_CONTROL register controls all attributes of the corresponding isochronous data flow that are independent from attributes of other isochronous data flows transmitted by that AV device.

The reception of an isochronous data flow through an input plug is controlled by one input plug control register (iPCR) and one input master plug register (iMPR) located on the receiving AV device. On each AV device there is only one INPUT\_MASTER\_PLUG register for all input plugs. The INPUT\_MASTER\_PLUG register controls all attributes that are common to all isochronous data flows received by the corresponding AV device. The INPUT\_PLUG\_CONTROL register controls all attributes of the corresponding isochronous data flow that are independent from attributes of other isochronous data flows received by that AV device.

An isochronous data flow can be controlled by any device connected to the IEEE 1394 bus by modifying the corresponding plug control registers. Plug control registers can be modified by means of asynchronous transactions on the IEEE 1394 bus or by internal modifications if the plug control registers are located on the controlling device.

The usage of plugs and plug control registers is illustrated in Figure 7.

Let  $\#iPCR$  and  $\#oPCR$  denote the number of isochronous data flows that can be simultaneously received and transmitted respectively by an AV device (such as a multiple viewing device or a multiple tuner device). Both  $\#iPCR$  and  $\#oPCR$  shall be constants in the range [0 to 31] that are AV device-dependent.

Each AV device shall implement  $\#oPCR$  output plugs, each controlled by one separate OUTPUT\_PLUG\_CONTROL register, and  $\#iPCR$  input plugs, each controlled by one separate INPUT\_PLUG\_CONTROL register. For AV devices implementing INPUT\_PLUG\_CONTROL registers, a single INPUT\_PLUG\_CONTROL register within that AV device shall be denoted as INPUT\_PLUG\_CONTROL[i], where  $i$  is in the range [0 to  $\#iPCR-1$ ]. The INPUT\_MASTER\_PLUG register is optional when  $\#iPCR = 0$  and required otherwise. For AV devices implementing OUTPUT\_PLUG\_CONTROL registers, a single OUTPUT\_PLUG\_CONTROL register within that AV device shall be denoted as OUTPUT\_PLUG\_CONTROL[i], where  $i$  is in the range [0 to  $\#oPCR-1$ ]. The OUTPUT\_MASTER\_PLUG register is optional if  $\#oPCR = 0$  and required otherwise.

The mapping between an INPUT\_PLUG\_CONTROL register and an isochronous data flow in a receiving AV device, and the mapping between an OUTPUT\_PLUG\_CONTROL register and an isochronous data flow in a transmitting AV device, are AV device-dependent.

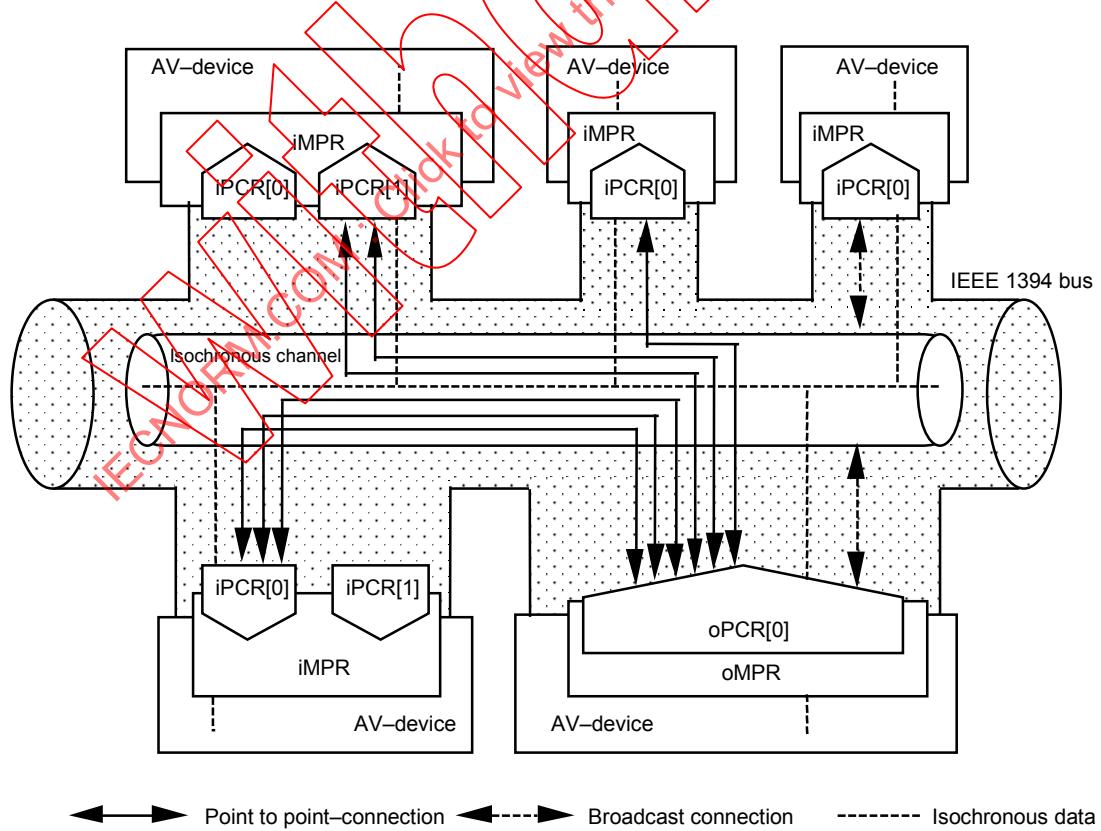

### 7.3 Connections

To transport isochronous data between two AV devices on the IEEE 1394 bus, it is necessary for an application to connect an output plug on the transmitting AV device to an input plug on the receiving AV device using one isochronous channel. The relationship between one input plug, one output plug and one isochronous channel is called a *point-to-point connection*. A point-to-point connection can only be broken by the same application that established it.

It is also possible that an application just starts the transmission or the reception of an isochronous data flow on its own AV device by connecting one of its output or input plugs respectively to an isochronous channel. The relationship between one output plug and one isochronous channel is called a *broadcast-out connection*. The relationship between one input plug and one isochronous channel is called a *broadcast-in connection*. Broadcast-out and broadcast-in connections are collectively called *broadcast connections*. A broadcast connection can be established only by the AV device on which the plug is located but it can be broken by any device. The concept of connections is illustrated in Figure 8.

Only one broadcast-out connection can exist in an output plug and only one broadcast-in connection can exist in an input plug. One broadcast connection and multiple point-to-point connections can exist simultaneously in one plug. This can be achieved by overlaying a connection over existing connections in the same input or output plug. Note that all connections that exist in one plug use the same isochronous channel and transport the same isochronous data flow. Multiple independent applications can create point-to-point connections between the same input and output plug.

#### 7.4 Plug states

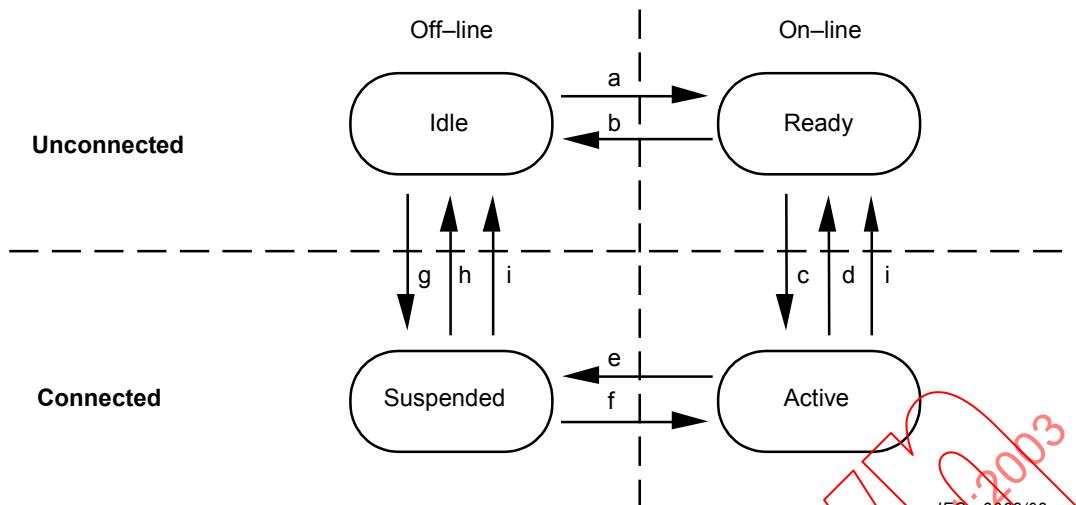

A plug can be in four states as described in Figure 9: idle, ready, active and suspended.

A plug is either *on-line* or *off-line*. Only a plug that is on-line is capable of transmitting or receiving an isochronous data flow.

NOTE 1 Being capable does not mean that the plug is actually transmitting or receiving an isochronous data flow.

A plug may be off-line, for example, because it relies on resources that are (temporarily) unpowered or otherwise unavailable.

NOTE 2 The reasons that cause a plug to switch between on- and off-line are internal to the AV device on which the plug is located and do not fall within the scope of this standard.

A plug to which no connections exist is called *unconnected*. A plug to which one or more connections exist is called *connected*. A plug that is connected and on-line is called *active*. Only an active plug shall transmit or receive an isochronous data flow except in the case of a bus reset where the isochronous data flow is resumed immediately after the bus-reset according to the procedures described in 7.10. A plug shall cease transmitting an isochronous data flow within 250 µs after becoming unconnected via transition d shown in Figure 9.

In Figure 9, all possible transitions from one state to another are given. Transitions are atomic and are effected by modifying the corresponding plug control register as described in 7.9.

NOTE 3 In order to ensure that the contents of plug registers are reliable, any intermediate results which may occur during a state transition should not be made available. A technique to achieve this is to disable access to the plug registers (for example by masking relevant interrupt mechanisms) once a state transition is invoked, and to ensure that the state transition is completed as an indivisible process without being interrupted, suspended or modified in any way. Under these conditions, a transition is said to be atomic.

#### 7.5 OUTPUT\_MASTER\_PLUG register definition

The format of the OUTPUT\_MASTER\_PLUG register is shown in Figure 10.

The number of output plug fields contains the number of output plugs an AV device implements as defined in 7.2.

The persistent and non-persistent extension fields are defined for future extensions.

The data rate capability is a constant, depending on the AV device concerned, that indicates the maximum speed at which an isochronous data flow can be transmitted by an AV device. The data rate capability is encoded as specified in Table 6.

The broadcast channel base determines the isochronous channel number when a broadcast-out connection is established to an output plug while there exists no point-to-point connection to that plug. The relationship between the broadcast channel base and the channel number is expressed in the following formula:

$B < 63: N[i] = (B+i) \bmod 63$

$B = 63: N[i] = 63$

where

$B$  is the value of broadcast channel base field;

$N[i]$  is the isochronous channel number for broadcast connection using `OUTPUT_PLUG_CONTROL[i]`.

In this way, the output plugs on an AV device use consecutive channel numbers if the broadcast channel base is not equal to 63 and they all use channel 63 if the broadcast channel base equals 63.

## 7.6 INPUT\_MASTER\_PLUG register definition

The format of the `INPUT_MASTER_PLUG` register is shown in Figure 11.

The number of input plugs contains the number of input plugs that an AV device implements, as defined in 7.2.

The persistent and non-persistent extension fields are defined for future extensions.

The data rate capability is a constant, depending on the AV device concerned, that indicates the maximum speed at which an isochronous data flow can be received by an AV device. The data rate capability is encoded as specified in Table 6.

## 7.7 OUTPUT\_PLUG\_CONTROL register definition

The format of the `OUTPUT_PLUG_CONTROL` register is shown in Figure 12.

The on-line bit always indicates whether the corresponding output plug is on-line (value one) or off-line (value zero).

The broadcast connection counter always indicates whether a broadcast-out connection to the output plug exists (value one) or not (value zero). The point-to-point connection counter always indicates the number of point-to-point connections that exist to the output plug.

For a suspended output plug, the channel indicates the channel number that the output plug shall use to transmit the isochronous data flow when it is activated. For an active output plug it indicates the actual channel number that the output plug uses to transmit the isochronous data flow. For an unconnected output plug it has no meaning.

For a suspended output plug, the data rate indicates the bit rate that the output plug shall use to transmit the isochronous packets of an isochronous data flow when it is activated. For an active output plug whose data rate value does not exceed the data rate capability of the `OUTPUT_MASTER_PLUG` register, it indicates the actual bit rate that the output plug uses to transmit the isochronous packets of an isochronous data flow. An active output plug whose data rate value exceeds the data rate capability of the `OUTPUT_MASTER_PLUG` register or indicates the value “reserved” (see Table 6) shall not transmit isochronous packets. For an unconnected plug, the data rate value is undefined. The data rate is encoded as an index in Table 6 that gives the corresponding IEEE 1394 bit rate value (see IEEE 1394).

The payload indicates the maximum number of quadlets that the output plug shall transmit in one isochronous packet of an isochronous data flow when it is activated. The value zero corresponds to 1 024 quadlets. The payload does not include the header, the header\_CRC and the data\_CRC that are required by IEEE 1394 to transmit an isochronous packet in addition to the data itself.

For an unconnected output plug, the overhead\_ID field specifies the upper bounds for the bandwidth that the output plug needs for the transmission of an isochronous packet of an isochronous data flow in addition to the bandwidth needed to transmit the payload of that isochronous packet. The overhead bandwidth serves to cope with delays caused by IEEE 1394 bus parameters. For a connected output plug, it indicates the bandwidth that has actually been allocated for this purpose. The overhead\_ID is encoded as an index in Table 7 that gives the corresponding overhead bandwidth in IEEE 1394 bandwidth units (see IEEE 1394).

The payload, data rate and overhead\_ID represent the associated bandwidth in IEEE 1394 bandwidth units (see IEEE 1394) for the output plug according to the following formula:

$$BWU = \text{overhead\_ID} \times C + (\text{payload} + K) \times DR \text{ if overhead\_ID} > 0;$$

$$BWU = 512 + (\text{payload} + K) \times DR \text{ if overhead\_ID} = 0;$$

where

$BWU$  = IEEE 1394 bandwidth units

$DR$  = data rate coefficient

$C$  = 32

$K$  = 3

$DR$  = 16 for S100

= 8 for S200

= 4 for S400

## 7.8 INPUT\_PLUG\_CONTROL register definition

The format of the INPUT\_PLUG\_CONTROL register is given in Figure 13.

The on-line bit always indicates whether the corresponding input plug is **on-line** (value one) or **off-line** (value zero).

The broadcast connection counter indicates whether a broadcast-in connection to the input plug exists (value one) or not (value zero). The point-to-point connection counter indicates the number of point-to-point connections that exist to the input plug.

For a connected input plug, the channel number indicates the actual channel number that the input plug uses to receive the isochronous data flow.

## 7.9 Plug control register modification rules

The contents of a plug control register shall be modified either internally by the AV device on which the plug control register is located or externally via the IEEE 1394 bus by using a quadlet compare\_swap lock transaction as defined in IEEE 1394. The effect of an external modification is specified as the “lock effect” in Figures 10 to 13 and described in 7.5 to 7.8. Internal modifications shall behave as a compare\_swap lock transaction as defined in IEEE 1394.

Each plug control register defined in 7.5 to 7.8 shall store any value according to the definition of write/lock effect if and only if the compare/swap lock transaction returns “resp\_complete”. A plug shall behave according to the requirements of 7.5 to 7.8 for the values that are stored in the plug control registers.

The following rule for modifying the contents of an INPUT\_MASTER\_PLUG register and OUTPUT\_MASTER\_PLUG register is specified:

- all modifications shall adhere to the definitions of the OUTPUT\_MASTER\_PLUG register and INPUT\_MASTER\_PLUG register as specified in 7.5 and 7.6 respectively.

The following rules for modifying the contents of an INPUT\_PLUG\_CONTROL register and OUTPUT\_PLUG\_CONTROL register are specified as follows:

- all modifications shall adhere to the definitions of the OUTPUT\_PLUG\_CONTROL register and INPUT\_PLUG\_CONTROL register as specified in 7.7 and 7.8 respectively;

- the channel and associated bandwidth (see 7.7) as stored in an OUTPUT\_PLUG\_CONTROL register shall be allocated during the entire time the corresponding output plug is connected;

- the channel number field and data rate field of an OUTPUT\_PLUG\_CONTROL register shall not be modified while the corresponding output plug is connected;

- the channel number field in an INPUT\_PLUG\_CONTROL register shall not be modified while its point-to-point connection counter field is not equal to zero;

- the broadcast connection counter field shall be set internally;

- when an output plug becomes connected, the data rate field, overhead ID field, channel number field, broadcast connection counter field and point-to-point connection counter field shall be modified in the same compare\_swap lock transaction;

- if the broadcast connection counter of an OUTPUT\_PLUG\_CONTROL register is modified from zero to one while its point-to-point connection counter remains set to zero, the channel number shall be modified in the same compare\_swap lock transaction according to the formula given in 7.5.

## 7.10 Bus reset

When a bus reset occurs, the following actions shall be performed.

- a) All AV devices that had connected input and output plugs prior to the bus reset shall continue respectively to receive and transmit the isochronous data flow immediately after the bus reset according to the values in the plug control registers immediately before the bus reset.

- b) AV devices that had not connected input and output plugs prior to the bus reset shall behave according to the values in the corresponding plug control registers after isoch\_resource\_delay (equal to 1,0 s) following the bus reset.

## 7.11 Plug control register access rules

The plug control registers occupy part of a node's address space, as shown by Figure 14.

An AV device shall support quadlet read and compare\_swap lock transactions on all quadlet-aligned addresses of the plug control registers that it implements (see 7.2). If a transaction is requested on the address of an unimplemented plug control register, the transaction may fail with the response code *resp\_address\_error* or behave as an unimplemented CSR, according, in either case, to IEEE 1394.

An AV device may optionally support a block read transaction on the plug control register address area. If such a block read transaction contains addresses of plug control registers that the AV device does not implement, the transaction shall either fail with the response code *resp\_address\_error* as defined in IEEE 1394, or succeed. If the transaction succeeds, the returned values for unimplemented plugs shall be consistent with the value of an unimplemented CSR according to IEEE 1394.

## 8 Connection management procedures (CMP)

### 8.1 Introduction

This clause describes the procedures that an application shall use to manage connections between input and output plugs of AV devices by modifying plug control registers according to the rules defined in Clause 7. Only connections as defined in Clause 7 of this standard can be managed. The following management procedures are defined for each connection type:

- establishing a connection;

- overlaying a connection;

- breaking a connection.

These operations involve the incrementing and decrementing of connection counters in the plug control registers. Figure 15 shows the relationship between these operations for the different connection types. The procedures for each connection type are described by flow diagrams in Figures 16 to 28. No change to the contents of a plug control register is executed until the first modify operation following it in the flow diagram. The flow diagrams represent possible implementations of the procedures. Other conforming implementations are possible. An implementation conforms if, and only if, it does not violate the plug control register modification rules (see 7.9) and the state transition diagram of Figure 15.

### 8.2 Managing point-to-point connections

Point-to-point connections are protected in the sense that a point-to-point connection can only be broken by the same application that established it. Consequently, the active output plug does not stop the transmission of the isochronous data flow as long as the application does not break its point-to-point connection to that output plug.

#### 8.2.1 Procedure for establishing a point-to-point connection

This procedure creates a protected connection between one unconnected input plug and one unconnected output plug using one unused channel. Figure 16 shows an implementation conforming to this procedure.

**NOTE** The choice of which OUTPUT\_PLUG\_CONTROL register and INPUT\_PLUG\_CONTROL register on the transmitting and receiving AV device respectively are used does not fall within the scope of this standard. The choice of which channel, data rate and overhead\_ID are used also does not fall within the scope of this standard.

#### 8.2.2 Procedure for overlaying a point-to-point connection

This procedure adds a protected connection to a connected output plug between that output plug and an input plug. The isochronous channel that the output plug is using to transmit the isochronous data flow shall be used for the added point-to-point connection. Figure 17 shows an implementation conforming to this procedure.

**NOTE** The choice of which INPUT\_PLUG\_CONTROL register on the receiving device is used does not fall within the scope of this standard.

#### 8.2.3 Procedure for breaking a point-to-point connection

This procedure deletes one protected connection between one connected input plug and one connected output plug. If breaking the point-to-point connection causes the output plug to become unconnected, the output plug shall stop transmitting the isochronous data flow. Figure 18 shows an implementation conforming to this procedure.

The responding application shall not reject the decrementing of the point-to-point connection counters in the OUTPUT\_PLUG\_CONTROL and INPUT\_PLUG\_CONTROL registers.

### 8.3 Managing broadcast-out connections

Broadcast-out connections are unprotected in the sense that a connection can be broken by any application. Consequently, the application that established the broadcast-out connection has no guarantee that the output plug will continue the transmission of the isochronous data flow. The following procedures are defined for a broadcast-out connection:

- establishing a broadcast-out connection;

- overlaying a broadcast-out connection;

- breaking a broadcast-out connection.

#### 8.3.1 Procedure for establishing a broadcast-out connection

This procedure creates an unprotected connection between one unused channel and one unconnected output plug. Figure 19 shows an implementation conforming to this procedure.

**NOTE** The choice of which OUTPUT\_PLUG\_CONTROL register on the transmitting AV device is used does not fall within the scope of this standard. The choice of which data rate and overhead\_ID are used does not fall within the scope of this standard.

The channel according to the formula in 7.5 shall be allocated. Note that if that channel is in use, the procedure fails.

#### 8.3.2 Procedure for overlaying a broadcast-out connection

This procedure adds an unprotected connection between a connected output plug and the channel that this output plug uses to transmit an isochronous data flow. Figure 20 shows an implementation conforming to this procedure.

#### 8.3.3 Procedure for breaking a broadcast-out connection

This procedure deletes an unprotected connection between a connected output plug and the channel that this output plug uses to transmit an isochronous data flow. If breaking the broadcast-out connection causes the output plug to become unconnected, the output plug shall stop transmitting the isochronous data flow. Figure 21 shows an implementation conforming to this procedure.

The responding application shall not reject the decrementing of the broadcast connection counter in the OUTPUT\_PLUG\_CONTROL register.

### 8.4 Managing broadcast-in connections

Broadcast-in connections are unprotected in the sense that the application that established the broadcast-in connection does not know whether there is an output plug transmitting an isochronous data flow on the channel that the input plug uses to receive and, if there is, there is no guarantee that the output plug will continue the transmission.

#### 8.4.1 Procedure for establishing a broadcast-in connection

This procedure creates an unprotected connection between one channel and one unconnected input plug. Figure 22 shows an implementation conforming to this procedure.

**NOTE** The choice of which INPUT\_PLUG\_CONTROL register on an AV device is used does not fall within the scope of this standard. The choice of which channel is used does not fall within the scope of this standard.

#### 8.4.2 Procedure for overlaying a broadcast-in connection

This procedure adds an unprotected connection between a connected input plug and the channel that this input plug uses to receive an isochronous data flow. Figure 23 shows an implementation conforming to this procedure.

#### 8.4.3 Procedure for breaking a broadcast-in connection

This procedure deletes an unprotected connection between a connected input plug and the channel that this input plug uses to receive an isochronous data flow. The input plug shall stop receiving the isochronous data flow if and only if breaking the broadcast-in connection causes the input plug to become unconnected. Figure 24 shows an implementation conforming to this procedure.

The responding application shall not reject the decrementing of the broadcast connection counter in the INPUT\_PLUG\_CONTROL register.

### 8.5 Managing connections after a bus reset

After a bus reset, all plugs are in the unconnected state. All procedures to restore the connections that existed in a plug immediately before the bus reset shall be executed before isoch\_resource\_delay following the bus reset to prevent the isochronous data flows being stopped (see 7.10). In these procedures, the channel and data\_rate used before the bus reset for the connection shall be used. Figure 25 shows the plug control register and isochronous data flow status after the bus reset.

#### 8.5.1 Procedure for restoring a point-to-point connection after a bus reset

Figure 26 shows an implementation conforming to the procedure to restore a point-to-point connection that it had established prior to the bus reset.

The channel and bandwidth that are to be allocated shall be calculated using the contents of the OUTPUT\_PLUG\_CONTROL register after the bus reset.

#### 8.5.2 Procedure for restoring a broadcast-out connection after a bus reset

Figure 27 shows an implementation conforming to the procedure to restore a broadcast-out connection that it had established prior to the bus reset.

The channel and bandwidth that are to be allocated shall be calculated using the contents of the OUTPUT\_PLUG\_CONTROL register after the bus reset.

#### 8.5.3 Procedure for restoring a broadcast-in connection after a bus reset

Figure 28 shows an implementation conforming to the procedure to restore a broadcast-in connection that it had established prior to the bus reset.

## 9 Function control protocol (FCP)

### 9.1 Introduction

Function control protocol (FCP) is designed to control devices connected through an IEEE 1394 bus. Various command sets and command transactions are available within FCP. FCP is based on IEEE 1394 and uses asynchronous packets of IEEE 1394 for sending commands and responses. See Figure 29.

A node that controls other node(s) by FCP commands is called a controller, and a node that is controlled by FCP commands is called a target.

An FCP frame is an entity of data to be transferred from a controller to a target or vice versa. An FCP frame that is sent from a controller to a target is called a command frame, and an FCP frame that is sent from a target to a controller is called a response frame. The register that is prepared for receiving a command frame is called a command register, and the register that is prepared for receiving a response frame is called a response register.

## 9.2 Asynchronous packet structure

The asynchronous packet structure used for sending an FCP frame is shown in Figures 30 and 31.

In FCP, the payloads of a write request for data block packet (refer to Figure 30) and a write request for data quadlet (refer to Figure 31) are called an FCP frame. A write request for data quadlet is used as an FCP frame only when the length of the FCP frame is exactly four bytes. FCP frames are classified as command frames and response frames. The command frame is written into a command register on a target and the response frame is written into a response register on a controller. These registers are separated and *destination\_offset* addresses of these registers are specified in the FCP as below.

Base address of FCP command register (offset)

FFFF F000 0B00<sub>16</sub>

Base address of FCP response register (offset)

FFFF F000 0D00<sub>16</sub>

Only write requests that specify FFFF F000 0B00<sub>16</sub> or FFFF F000 0D00<sub>16</sub> as the *destination\_offset* are permitted.

## 9.3 FCP frame structure

The FCP frame structure is shown in Figure 32.

Command/Transaction Set (CTS) is one component of an FCP frame. CTS specifies the command set, the structure of the command/response field and the rules of transactions used for sending commands and responses. The CTS table is shown in Table 8.

### 9.3.1 Vendor unique command/transaction set

If the CTS code is 1110<sub>2</sub>, it indicates that the FCP frame belongs to vendor unique CTS. An FCP frame structure that belongs to vendor unique CTS is shown in Figure 33.

Each vendor may specify a frame structure (except company\_ID), a command set and rules for sending commands/responses.

### 9.3.2 Extended command/transaction set

CTS code 1111<sub>2</sub> is reserved for future extensions of CTS.

**Table 1 – Code allocation of FN**

| <b>FN</b> | <b>Description</b>             |

|-----------|--------------------------------|

| $00_2$    | Not divided                    |

| $01_2$    | Divided into two data blocks   |

| $10_2$    | Divided into four data blocks  |

| $11_2$    | Divided into eight data blocks |

**Table 2 – Placing of data block sequence**

| <b>FN</b> | <b>Bits of DBC showing the place of data block sequence</b> |

|-----------|-------------------------------------------------------------|

| $00_2$    | (Not divided)                                               |

| $01_2$    | Shown in the lowest 1 bit                                   |

| $10_2$    | Shown in the lowest 2 bits                                  |

| $11_2$    | Shown in the lowest 3 bits                                  |

**Table 3 – Code allocation of FMT**

| <b>FMT</b>                         | <b>Description</b>     |

|------------------------------------|------------------------|

| $00\ 0000_2$                       | DVCR                   |

| $00\ 0001_2$<br>to<br>$00\ 1111_2$ | Reserved               |

| $01\ 0000_2$                       | Audio and music        |

| $01\ 0001_2$<br>to<br>$01\ 1101_2$ | Reserved               |

| $01\ 1110_2$                       | Free (vendor unique)   |

| $01\ 1111_2$                       | Reserved               |

| $10\ 0000_2$                       | MPEG2-TS               |

| $10\ 0001_2$                       | ITU-R B0.1294 System B |

| $10\ 0010_2$<br>to<br>$10\ 1101_2$ | Reserved               |

| $11\ 1110_2$                       | Free (vendor unique)   |

| $11\ 1111_2$                       | No data                |

**Table 4 – Time stamp field of source packet header**

| Time stamp field                                                     |                                                                   | Description    |

|----------------------------------------------------------------------|-------------------------------------------------------------------|----------------|

| Higher 13 bits                                                       | Lower 12 bits                                                     |                |

| 0 0000 0000 0000 <sub>2</sub><br>to<br>0 1111 0011 1111 <sub>2</sub> | 0000 0000 0000 <sub>2</sub><br>and<br>1011 1111 1111 <sub>2</sub> | Time stamp     |

| 1 1111 1111 1111 <sub>2</sub>                                        | and<br>1111 1111 1111 <sub>2</sub>                                | No information |

| Other values                                                         |                                                                   | Reserved       |

**Table 5 – Time stamp of SYT field**

| SYT                                          |                                                                   | Description    |

|----------------------------------------------|-------------------------------------------------------------------|----------------|

| Higher 4 bits                                | Lower 12 bits                                                     |                |

| 0000 <sub>2</sub><br>to<br>1111 <sub>2</sub> | 0000 0000 0000 <sub>2</sub><br>and<br>1011 1111 1111 <sub>2</sub> | Time stamp     |

| 1111 <sub>2</sub>                            | and<br>1111 1111 1111 <sub>2</sub>                                | No information |

| Other values                                 |                                                                   | Reserved       |

**Table 6 – oMPR and iMPR data rate capability and OPCR data rate encoding**

| Data rate<br>(or capability) | IEEE 1394 speed |

|------------------------------|-----------------|

| 00 <sub>2</sub>              | S100            |

| 01 <sub>2</sub>              | S200            |

| 10 <sub>2</sub>              | S400            |

| 11 <sub>2</sub>              | Reserved        |

**Table 7 – oPCR overhead ID encoding**

| Overhead ID | IEEE 1394 bandwidth allocation units |

|-------------|--------------------------------------|

| $0000_2$    | 512                                  |

| $0001_2$    | 32                                   |

| $0010_2$    | 64                                   |

| $0011_2$    | 96                                   |

| $0100_2$    | 128                                  |

| $0101_2$    | 160                                  |

| $0110_2$    | 192                                  |

| $0111_2$    | 224                                  |

| $1000_2$    | 256                                  |

| $1001_2$    | 288                                  |

| $1010_2$    | 320                                  |

| $1011_2$    | 352                                  |

| $1100_2$    | 384                                  |

| $1101_2$    | 416                                  |

| $1110_2$    | 448                                  |

| $1111_2$    | 480                                  |

**Table 8 – CTS: Command/transaction set encoding**

| CTS code                   | Command/transaction set |

|----------------------------|-------------------------|

| $0000_2$                   | AV/C                    |

| $0001_2$                   | Reserved for CAL        |

| $0010_2$                   | Reserved for EHS        |

| $0011_2$                   | HAVi                    |

| $0100_2$                   | Automotive              |

| $0101_2$                   | Reserved                |

| $1110_2$<br>to<br>$1101_2$ | Vendor unique           |

| $0110_2$<br>to<br>$1101_2$ | Reserved                |

| $1111_2$                   | Extended CTS            |

**Table 9 – Unit\_SW\_Version code assignment**

| <b>Unit_SW_Version</b> | <b>Command/transaction set</b>      |

|------------------------|-------------------------------------|

| 01 00 00 <sub>16</sub> | Reserved                            |

| 01 00 01 <sub>16</sub> | AV/C protocol                       |

| 01 00 02 <sub>16</sub> | Reserved for standardization by CAL |

| 01 00 04 <sub>16</sub> | Reserved for standardization by EHS |

| 01 00 08 <sub>16</sub> | HAVi protocol                       |

| 01 00 0A <sub>16</sub> | Automotive                          |

| 01 40 00 <sub>16</sub> | Vendor unique                       |

| 01 40 01 <sub>16</sub> | Vendor unique                       |

| Other values           | Reserved for future standardization |

IECNORM.COM : Click to view the full PDF of IEC 61883-1:2003

| Offset (Base address FFFF F000 0000 <sub>16</sub> ) |                           |                       |                              |

|-----------------------------------------------------|---------------------------|-----------------------|------------------------------|

| <b>Bus_info_block</b>                               |                           |                       |                              |

| 04 00 <sub>16</sub>                                 | 04 <sub>16</sub>          | crc_length            | rom_crc_value                |

| 04 04 <sub>16</sub> " 1 3 9 4                       |                           |                       |                              |

| 04 08 <sub>16</sub>                                 | lrmc<br>cmc<br>isc<br>bmc | Reserved              | cyc_clk_acc max_rec Reserved |

| 04 0C <sub>16</sub>                                 | node_vendor_id            |                       | chip_id_hi                   |

| 04 10 <sub>16</sub>                                 | chip_id_lo                |                       |                              |

| <b>Root_directory</b>                               |                           |                       |                              |

| 04 14 <sub>16</sub>                                 | root_length               |                       | CRC                          |

| 04 18 <sub>16</sub>                                 | 03 <sub>16</sub>          | module_vendor_id      |                              |

| 04 1C <sub>16</sub>                                 | 0C <sub>16</sub>          | node_capabilities     |                              |

| 04 20 <sub>16</sub>                                 | 8D <sub>16</sub>          | node_unique_id_offset |                              |

| 04 24 <sub>16</sub>                                 | D1 <sub>16</sub>          | unit_directory_offset |                              |

| 04 28 <sub>16</sub>                                 | :                         |                       |                              |

|                                                     |                           | Optional              |                              |

| <b>Unit_directory</b>                               |                           |                       |                              |

|                                                     |                           | unit_directory_length |                              |

|                                                     |                           | CRC                   |                              |

|                                                     |                           | 12 <sub>16</sub>      | unit_spec_id                 |

|                                                     |                           | 13 <sub>16</sub>      | unit_sw_version              |

|                                                     |                           | Optional              |                              |

| <b>Node_unique_id leaf</b>                          |                           |                       |                              |

|                                                     |                           | 00 02 <sub>16</sub>   |                              |

|                                                     |                           | CRC                   |                              |

|                                                     |                           | node_vendor_id        |                              |

|                                                     |                           | chip_id_hi            |                              |

|                                                     |                           | chip_id_lo            |                              |

Figure 1 – Configuration ROM

Figure 2 – Isochronous packet

Figure 3 – CIP header

Figure 4 – Model of transmission of source packets

Figure 5a – CIP header with SYT field

Figure 5b – CIP header without SYT field

Figure 5 – Two quadlets CIP header (Form\_0, Form\_1=0)

Figure 6 – Source packet header format

Figure 7 – Plug and PR usage

Figure 8 – Connections

**Key**

- a triggered internally; no action

- b triggered internally; no action

- c triggered by establishing the first connection; start isochronous data flow transmission/reception

- d triggered by breaking the last connection; stop isochronous data flow transmission/reception

- e triggered internally; suspend isochronous data flow transmission/reception

- f triggered internally; resume isochronous data flow transmission/reception

- g triggered by establishing the first connection; no action

- h triggered by breaking the last connection; no action

- i triggered by bus reset; for actions see 7.10

**Figure 9 – Plug state diagram****Definition**

| Data rate capability | Broadcast channel base | Non-persistent extension field | Persistent extension field | Reserved | Number of output plugs |

|----------------------|------------------------|--------------------------------|----------------------------|----------|------------------------|

| 2                    | 6                      | 8                              | 8                          | 3        | 5                      |

**Initial values**

|                  |      |                  |       |       |

|------------------|------|------------------|-------|-------|

| Vendor dependent | Ones | Vendor dependent | Zeros | #oPCR |

|------------------|------|------------------|-------|-------|

**Bus reset and command reset values**

|           |      |           |       |       |

|-----------|------|-----------|-------|-------|

| Unchanged | Ones | Unchanged | Zeros | #oPCR |

|-----------|------|-----------|-------|-------|

**Read value**

|             |                      |       |       |

|-------------|----------------------|-------|-------|

| Last update | Last successful lock | Zeros | #oPCR |

|-------------|----------------------|-------|-------|

**Lock effect**

|         |                       |         |

|---------|-----------------------|---------|

| Ignored | Conditionally written | Ignored |

|---------|-----------------------|---------|

IEC 3069/02

**Figure 10 – oMPR format**

**Definition**

|                      |          |                                |                            |          |                       |

|----------------------|----------|--------------------------------|----------------------------|----------|-----------------------|

| Data rate capability | Reserved | Non-persistent extension field | Persistent extension field | Reserved | Number of input plugs |

| 2                    | 6        | 8                              | 8                          | 3        | 5                     |

**Initial values**

|                  |       |      |                  |       |       |

|------------------|-------|------|------------------|-------|-------|

| Vendor dependent | Zeros | Ones | Vendor dependent | Zeros | #iPCR |

|------------------|-------|------|------------------|-------|-------|

**Bus reset and command reset values**

|           |       |      |           |       |       |

|-----------|-------|------|-----------|-------|-------|

| Unchanged | Zeros | Ones | Unchanged | Zeros | #iPCR |

|-----------|-------|------|-----------|-------|-------|

**Read value**

|             |       |                      |       |       |

|-------------|-------|----------------------|-------|-------|

| Last update | Zeros | Last successful lock | Zeros | #iPCR |

|-------------|-------|----------------------|-------|-------|

**Lock effect**

|         |                       |         |

|---------|-----------------------|---------|

| Ignored | Conditionally written | Ignored |

|---------|-----------------------|---------|

IEC 3070/02

**Figure 11 – iMPR format****Definition**

|         |                              |                                   |          |                |           |             |         |

|---------|------------------------------|-----------------------------------|----------|----------------|-----------|-------------|---------|

| On-line | Broadcast connection counter | Point-to-point connection counter | Reserved | Channel number | Data rate | Overhead ID | Payload |

| 1       | 1                            | 6                                 | 2        | 6              | 2         | 4           | – 10    |

**Initial values**

|       |

|-------|

| Zeros |

|-------|

**Bus reset and command reset values**

|           |       |           |       |           |

|-----------|-------|-----------|-------|-----------|

| Unchanged | Zeros | Unchanged | Zeros | Unchanged |

|-----------|-------|-----------|-------|-----------|

**Read value**

|             |                      |       |                      |             |

|-------------|----------------------|-------|----------------------|-------------|

| Last update | Last successful lock | Zeros | Last successful lock | Last update |

|-------------|----------------------|-------|----------------------|-------------|

**Lock effect**

|         |                       |         |                       |         |

|---------|-----------------------|---------|-----------------------|---------|

| Ignored | Conditionally written | Ignored | Conditionally written | Ignored |

|---------|-----------------------|---------|-----------------------|---------|

IEC 3071/02

**Figure 12 – oPCR format**

| Definition                         |                              |                                   |                       |                  |          |

|------------------------------------|------------------------------|-----------------------------------|-----------------------|------------------|----------|

| On-line                            | Broadcast connection counter | point-to-point connection counter | Reserved              | Channel number   | Reserved |

| 1                                  | 1                            | 6                                 | 2                     | 6                | 16       |

| Initial values                     |                              |                                   |                       |                  |          |

| Zeros                              |                              |                                   |                       |                  |          |

| Bus reset and command reset values |                              |                                   |                       |                  |          |

| Unchanged                          | Zeros                        | Unchanged                         | Zeros                 | IEC 61883-1:2003 |          |

| Read value                         |                              |                                   |                       |                  |          |

| Last update                        | Last successful lock         | Zeros                             | Last successful lock  | Zeros            |          |

| Lock effect                        |                              |                                   |                       |                  |          |

| Ignored                            | Conditionally written        | Ignored                           | Conditionally written | Ignored          |          |

IEC 3072/02

Figure 13 – iPCR format

IEC 3073/02

Figure 14 – PCR address map

**Key**

- a establishing a point-to-point connection; permitted by any application

- b overlaying a point-to-point connection; permitted by any application

- c breaking a point-to-point connection; permitted by an application that has previously established or overlaid a point-to-point connection

- d establishing a broadcast connection; permitted by an application located on the device where the PCR is located